SD16 Operation

21-13SD16

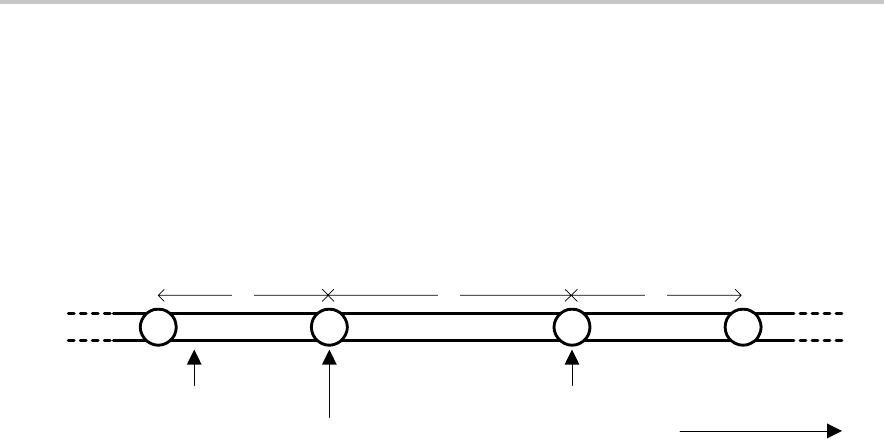

21.2.9 Conversion Operation Using Preload

When multiple channels are grouped the SD16PREx registers can be used to

delay the conversion time frame for each channel. Using SD16PREx, the

decimation time of the digital filter is increased by the specified number of f

M

clock cycles and can range from 0 to 255. Figure 21−8 shows an example

using SD16PREx.

Figure 21−8. Conversion Delay using Preload

Conversion

32

SD16OSRx = 32

Load SD16PREx:

SD16PREx = 8

Preload

applied

Time

Delayed Conversion

40

Delayed Conversion

Result

Conversion

32

f

M

cycles:

The SD16PREx delay is applied to the beginning of the next conversion cycle

after being written. The delay is used on the first conversion after SD16SC is

set and on the conversion cycle following each write to SD16PREx. Following

conversions are not delayed. After modifying SD16PREx, the next write to

SD16PREx should not occur until the next conversion cycle is completed,

otherwise the conversion results may be incorrect.

The accuracy of the result for the delayed conversion cycle using SD16PREx

is dependent on the length of the delay and the frequency of the analog signal

being sampled. For example, when measuring a DC signal, SD16PREx delay

has no effect on the conversion result regardless of the duration. The user

must determine when the delayed conversion result is useful in their

application.

Figure 21−9 shows the operation of grouped channels 0 and 1. The preload

register of channel 1 is loaded with zero resulting in immediate conversion

whereas the conversion cycle of channel 0 is delayed by setting SD16PRE0

= 8. The first channel 0 conversion uses SD16PREx = 8, shifting all

subsequent conversions by 8 f

M

clock cycles.