Scan IF Registers

24-44 Scan IF

SIFCTL3, Scan IF Control Register 3

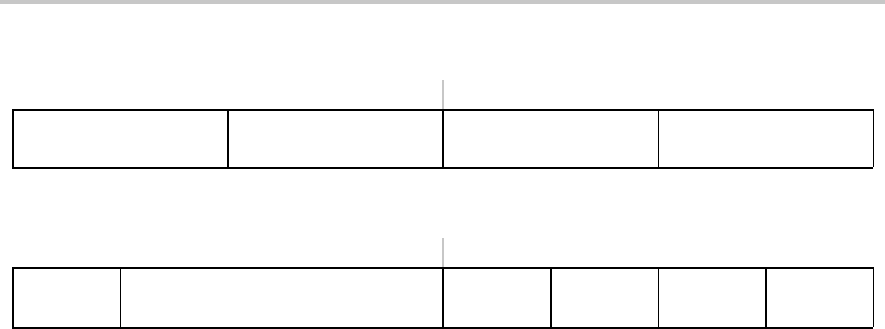

15 14 13 12 11 10 9 8

SIFS2x SIFS1x SIFIS2x SIFIS1x

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

76543210

SIFCS SIFIFGSETx SIF3OUT SIF2OUT SIF1OUT SIF0OUT

rw−(0) rw−(0) rw−(0) rw−(0) r−(0) r−(0) r−(0) r−(0)

SIFS2x

Bits

15-14

S2 source select. These bits select the S2 source for the PSM when SIFCS

= 1.

00 SIF0OUT is the S2 source.

01 SIF1OUT is the S2 source.

10 SIF2OUT is the S2 source.

11 SIF3OUT is the S2 source.

SIFS1x

Bits

13-12

S1 source select. These bits select the S1 source fro the PSM when SIFCS

= 1.

00 SIF0OUT is the S1 source.

01 SIF1OUT is the S1 source.

10 SIF2OUT is the S1 source.

11 SIF3OUT is the S1 source.

SIFIS2x

Bits

11-10

SIFIFG4 interrupt flag source

00 SIFIFG4 is set with each count of SIFCNT2.

01 SIFIFG4 is set if (SIFCNT2 modulo 4) = 0.

10 SIFIFG4 is set if (SIFCNT2 modulo 64) = 0.

11 SIFIFG4 is set when SIFCNT2 decrements from 01h to 00h.

SIFIS1x

Bits

9-8

SIFIFG3 interrupt flag source

00 SIFIFG3 is set with each count, up or down, of SIFCNT1.

01 SIFIFG3 is set if (SIFCNT1 modulo 4) = 0.

10 SIFIFG3 is set if (SIFCNT1 modulo 64) = 0.

11 SIFIFG3 is set when SIFCNT1 rolls over from 0FFh to 00h.

SIFCS

Bit 7 Comparator output/Timer_A input selection

0 The SIFEX(tsm) signal and the comparator output are connected to the

TACCRx inputs.

1 The SIFxOUT outputs are connected to the TACCRx inputs selected

with the SIFS1x and SIFS2x bits.