Scan IF Operation

24-14 Scan IF

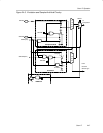

24.2.2 Scan IF Timing State Machine

The TSM is a sequential state machine that cycles through the SIFTSMx

registers and controls the analog front end and sensor excitation automatically

with no CPU intervention. The states are defined within a 24 x 16-bit memory,

SIFTSM0 to SIFTSM23. The SIFEN bit enables the TSM. When SIFEN = 0,

the ACLK input divider, the TSM start flip-flop, and the TSM outputs are reset

and the internal oscillator is stopped. The TSM block diagram is shown in

Figure 24−8.

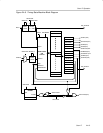

The TSM begins at SIFTSM0 and ends when the TSM encounters a SIFTSMx

state with a set SIFTSTOP bit. When a state with a set SIFSTOP bit is reached,

the state counter is reset to zero and state processing stops. State processing

re-starts at SIFTSM0 with the next start condition when SIFTSMRP = 0, or

immediately when SIFTSMRP = 1

After generation of the SIFSTOP(tsm) pulse, the timing state machine will load

and maintain the conditions defined in SIFTSM0. In this state SIFLCEN(tsm)

should be reset to ensure that all LC oscillators are shorted.