Theory of Operation

3–44

1780R-Series Service Manual

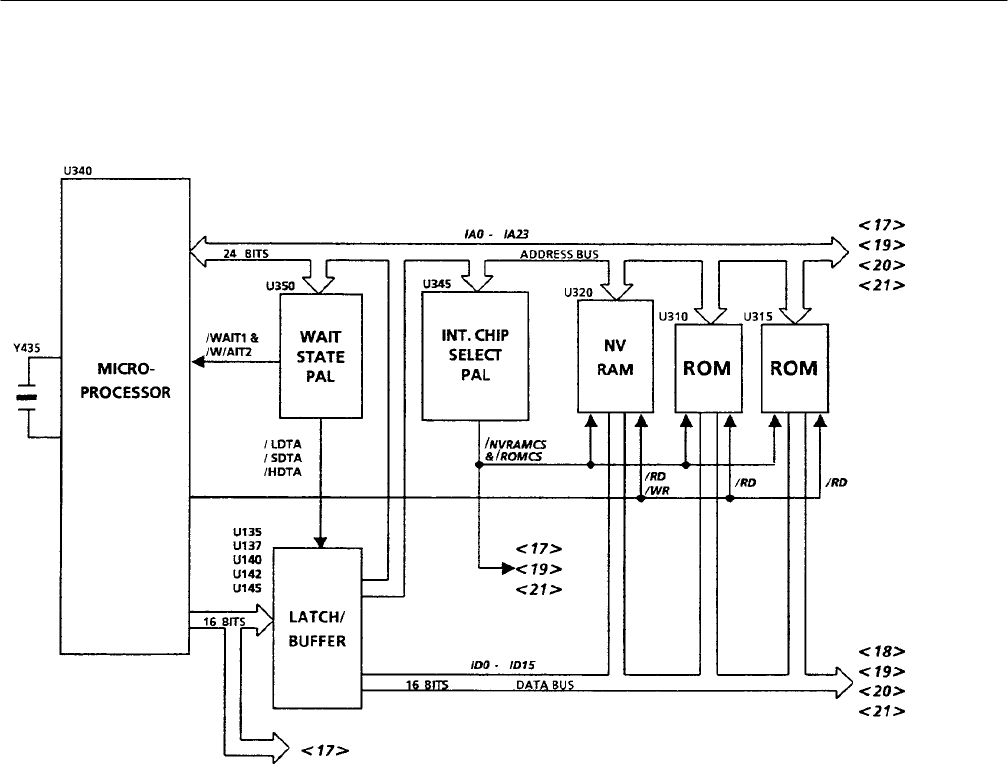

Diagrams 16 & 17 Master MPU, ROM & NVRAM

The Master MPU kernel consists of the NS32CG16 processor, running at

10 MHz, and its associated clock, memory, and buffering circuitry. Also included

here are the Internal Chip Select and Wait State Generator PALs. The Master

MPU is supported with 128K of Read-Only Memory (ROM), a Non-Volatile

Random Access Memory (NVRAM), and 128K of Dynamic Random Access

Memory (DRAM), shown on Diagram 17.

Microprocessor. The heart of the Master MPU system is the Microprocessor,

U340, running at 10 MHz after the 20 MHz output of the crystal oscillator,

Y435, is divided down. FCLK, which is derived from the crystal oscillator, is

output to U361 (the Dynamic RAM control PAL) on Diagram 17. The Master

MPU is reset at power up by U344 and a segment of R360 to allow the

instrument power supplies to stabilize. It can be reset at any time by momentari-

ly shorting J344. U535A and B is a 74LS74 flip-flop that provides metastable

protection for the processor /INT and /HOLD signals.

Overview

Circuit Theory