Theory of Operation

3–46

1780R-Series Service Manual

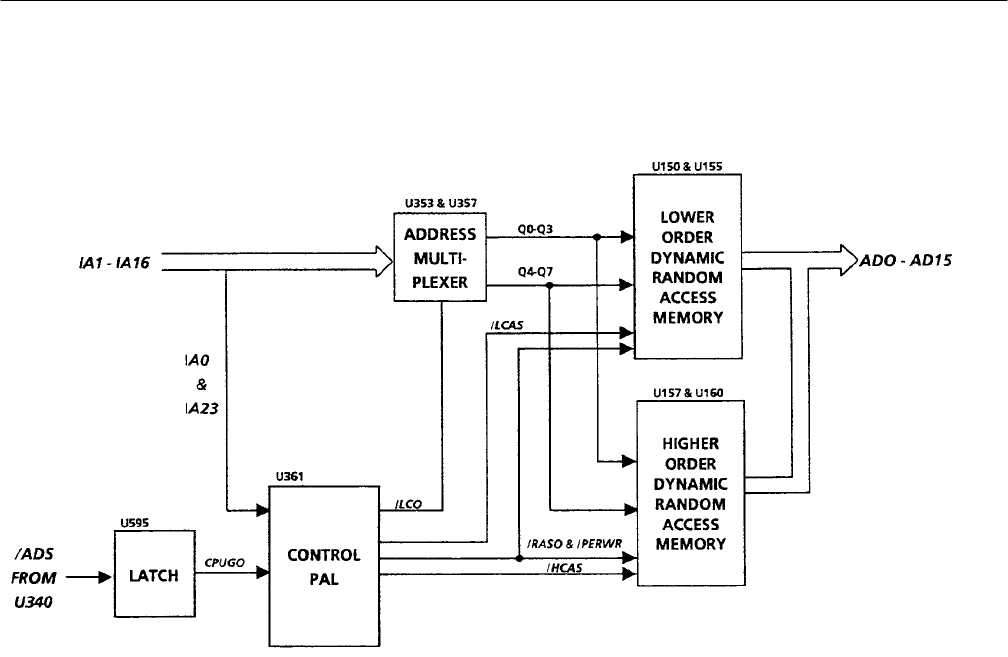

Diagram 17 Dynamic RAM

The Dynamic Random Access Memory (DRAM) is a 16-bit wide memory used

by the readout engine for its instructions. The system consists of three major

components; the memory array, an address multiplexer, and a control PAL. The

memory array consists of four 4-bit architecture DRAM chips residing on a

16-bit bus.

The Master MPU accesses each address from IA1 through IA8 (256 values) once

every 4 ms; the least significant bit (IA0) is not used as an address.

Address Multiplexer. The Address Multiplexer consists of two 74ALS158 (Quad

2-to-1 Multiplexers U353 & U357) that produce a combined set of RAS/ CAS

enables for the memory chips. Quad NAND gate U450 is mounted on the circuit

board but is not used in the current memory configuration. The order of

addresses multiplexed is chosen so that the lower order addresses (IA1 etc.) are

used as RAS addresses to allow for DRAM refresh by accessing a 512-word

address space.

DRAM Control PAL. The heart of the DRAM control circuit is a PAL, U361. It

provides all the timing signals for Master MPU and DMA accesses, along with

reshaping the write enable (/PERWR) used by the external interface and the

DRAM chips.

Overview

Circuit Theory