User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 120 of 377

gx_02.fm.(1.2)

March 27, 2006

Translation Lookaside Buffer Management Instructions—(OEA)

The address-translation mechanism is defined in terms of the segment descriptors and page table entries

(PTEs) PowerPC processors use to locate the logical-to-physical address mapping for a particular access.

These segment descriptors and PTEs reside in Segment Registers and page tables in memory, respectively.

See Chapter 7, Signal Descriptions, on page 249 for more information about TLB operations. Table 2-45

summarizes the operation of the TLB instructions in the 750GX.

Implementation Note: The tlbia instruction is optional for an implementation if its effects can be achieved

through some other mechanism. Therefore, it is not implemented on the 750GX. As described above, tlbie

can be used to invalidate a particular index of the TLB based on EA[14–19]—a sequence of 64 tlbie instruc-

tions followed by a tlbsync instruction invalidates all the TLB structures (for EA[14–19] = 0, 1, 2,..., 63).

Attempting to execute tlbia causes an illegal instruction program exception.

The presence and exact semantics of the TLB management instructions are implementation-dependent. To

minimize compatibility problems, system software should incorporate uses of these instructions into subrou-

tines.

2.3.7 Recommended Simplified Mnemonics

To simplify assembly language coding, a set of alternative mnemonics is provided for some frequently used

operations (such as no-op, load immediate, load address, move register, and complement register).

Programs written to be portable across the various assemblers for the PowerPC Architecture should not

assume the existence of mnemonics not described in this document.

For a complete list of simplified mnemonics, see Appendix F, “Simplified Mnemonics” in the PowerPC Micro-

processor Family: The Programming Environments Manual.

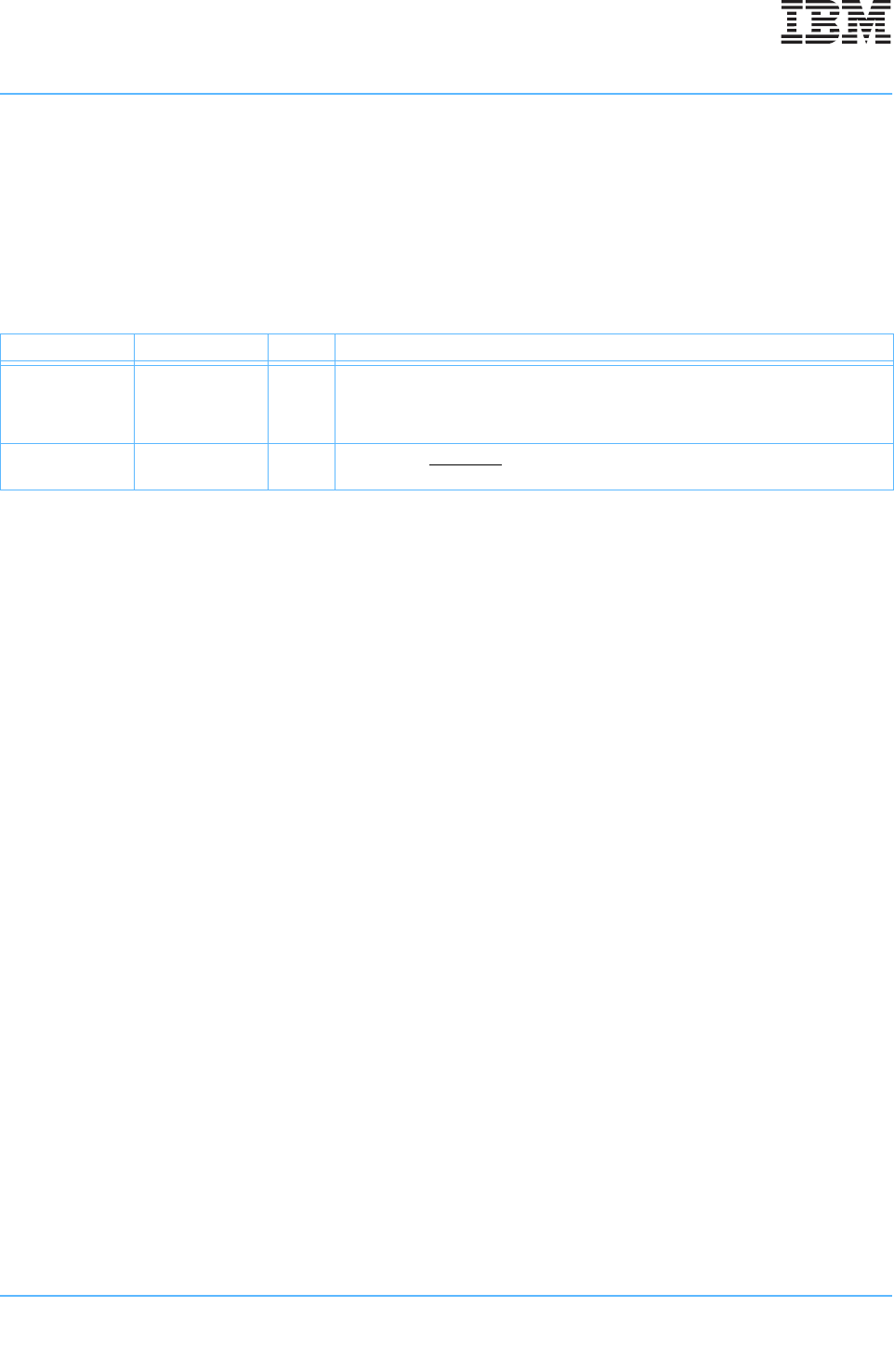

Table 2-45. Translation Lookaside Buffer Management Instruction

Name Mnemonic Syntax Implementation Notes

TLB Invalidate

Entry

tlbie rB

Invalidates both ways in both instruction and data TLB entries at the index provided

by EA[14–19]. It executes regardless of the MSR[DR] and MSR[IR] settings. To

invalidate all entries in both TLBs, the programmer should issue 64 tlbie instruc-

tions; each should successively increment this field.

TLB Synchronize tlbsync —

On the 750GX, the only function tlbsync serves is to wait for the TLB Invalidate

Synchronize (TLBISYNC

) signal to go inactive.