User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Signal Descriptions

Page 256 of 377

gx_07.fm.(1.2)

March 27, 2006

7.2.4.1 Transfer Type (TT[0–4])

The transfer type (TT[0–4]) signals consist of five input/output signals on the 750GX. For a complete descrip-

tion of TT[0–4] signals and for transfer type encodings, see Table 7-1.

Transfer Type (TT[0–4])—Output

Transfer Type (TT[0–4])—Input

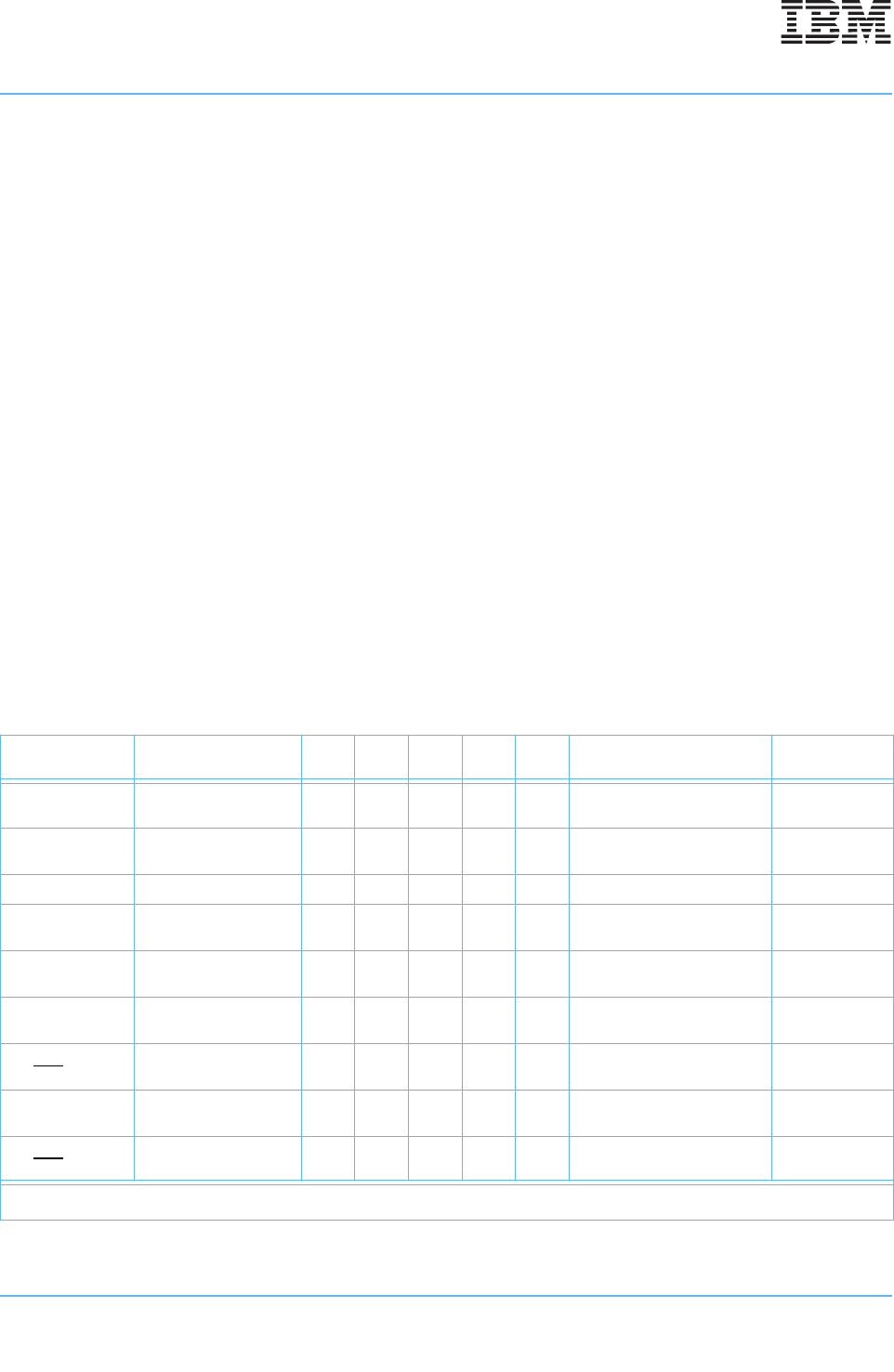

Table 7-1 describes the transfer encodings for the 750GX bus master.

State Asserted/

Negated

Indicates the type of transfer in progress.

Timing Assertion/

Negation/

High

Impedance

The same as A[0–31].

State Asserted/

Negated

Indicates the type of transfer in progress (see Table 7-1).

Timing Assertion/

Negation

The same as A[0–31].

Table 7-1. Transfer Type Encodings for PowerPC 750GX Bus Master

(Page 1 of 2)

750GX Bus

Master Transaction

Transaction Source TT0 TT1 TT2 TT3 TT4

60x Bus Specification

Command

Transaction

Address only

1

Data Cache Block Store

(dcbst)

00000Clean block Address only

Address only

1

Data Cache Block Flush

(dcbf)

00100Flush block Address only

Address only

1

Synchronize (sync) 01000sync Address only

Address only

Data Cache Block Set

to Zero (dcbz)

01100Kill block Address only

Address only

1

Data Cache Block Inval-

idate (dcbi)

01100Kill block Address only

Address only

1

Enforce In-Order Exe-

cution of I/O (eieio)

10000eieio Address only

Single-beat write

(nonGBL

)

External Control Out

Word Indexed (ecowx)

10100External control word writeSingle-beat write

N/A N/A 11000

Translation Lookaside Buffer

(TLB) invalidate

Address only

Single-beat read

(nonGBL

)

External Control In

Word Indexed (eciwx)

11100External control word readSingle-beat read

1. Address-only transaction occurs if enabled by setting the HID0[ABE] bit to 1.