User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

Exceptions

Page 168 of 377

gx_04.fm.(1.2)

March 27, 2006

A TEA indication on the bus can result from any load or store operation initiated by the processor. In general,

TEA

is expected to be used by a memory controller to indicate that a memory parity error or an uncorrectable

memory ECC error has occurred. Note that the resulting machine-check exception is imprecise and unor-

dered with respect to the instruction that originated the bus operation.

If MSR[ME] and the appropriate HID0 bits are set, the exception is recognized and handled; otherwise, the

processor generates an internal checkstop condition. When the exception is recognized, all incomplete stores

are discarded. The bus protocol operates normally.

A machine-check exception might result from referencing a nonexistent physical address, either directly (with

MSR[DR] = 0) or through an invalid translation. If a dcbz instruction introduces a block into the cache associ-

ated with a nonexistent physical address, a machine-check exception can be delayed until an attempt is

made to store that block to main memory. Not all PowerPC processors provide the same level of error

checking. Checkstop sources are implementation-dependent.

Machine-check exceptions are enabled when MSR[ME] = 1; this is described in the next section. If MSR[ME]

= 0 and a machine check occurs, the processor enters the checkstop state. The checkstop state is described

in Section 4.5.2.2, Checkstop State (MSR[ME] = 0), on page 169.

4.5.2.1 Machine-Check Exception Enabled (MSR[ME] = 1)

Machine-check exceptions are enabled when MSR[ME] = 1. When a machine-check exception is taken,

registers are updated as shown in Table 4-9.

The machine-check exception is usually unrecoverable in the sense that execution cannot resume in the

context that existed before the exception (see Section 4.3.6, Setting MSR[RI],). If the condition that caused

the machine check does not otherwise prevent continued execution, MSR[ME] is set to allow the processor to

continue execution at the machine-check exception vector address and prevent the processor from entering

checkstop state if another machine check occurs. Typically, earlier processes cannot resume. However,

operating systems can use the machine-check exception handler to try to identify and log the cause of the

machine-check condition.

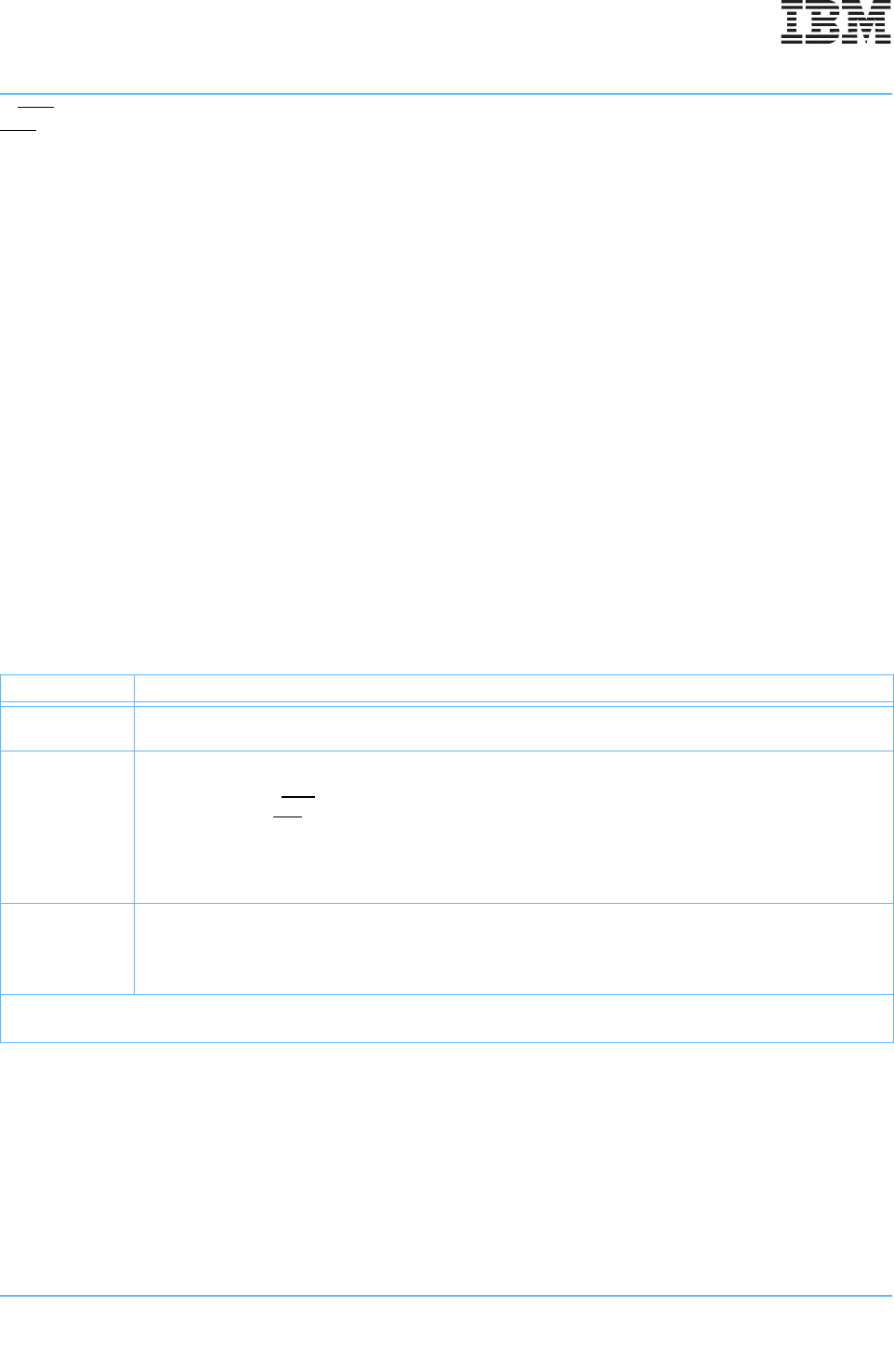

Table 4-9. Machine-Check Exception—Register Settings

Register Setting Description

SRR0

On a best-effort basis, the 750GX can set this to an EA of some instruction that was executing or about to be exe-

cuting when the machine-check condition occurred.

SRR1

0:10 Cleared.

11 Set when an L2 data-cache ECC double-bit error is detected; otherwise, zero.

12 Set when an M

CP signal is asserted; otherwise, zero.

13 Set when a T

EA signal is asserted; otherwise, zero.

14 Set when a data-bus parity error is detected; otherwise, zero.

15 Set when an address-bus parity error is detected; otherwise, zero.

16:31 MSR[16–31].

MSR

POW 0

ILE —

EE 0

PR 0

FP 0

ME 0

FE0 0

SE 0

BE 0

FE1 0

IP —

IR 0

DR 0

PM 0

RI 0

LE Set to value of ILE

Note: To handle another machine-check exception, the exception handler should set MSR[ME] as soon as it is practical after a

machine-check exception is taken. Otherwise, subsequent machine-check exceptions cause the processor to enter the checkstop state.