User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_11.fm.(1.2)

March 27, 2006

Performance Monitor and System Related Features

Page 353 of 377

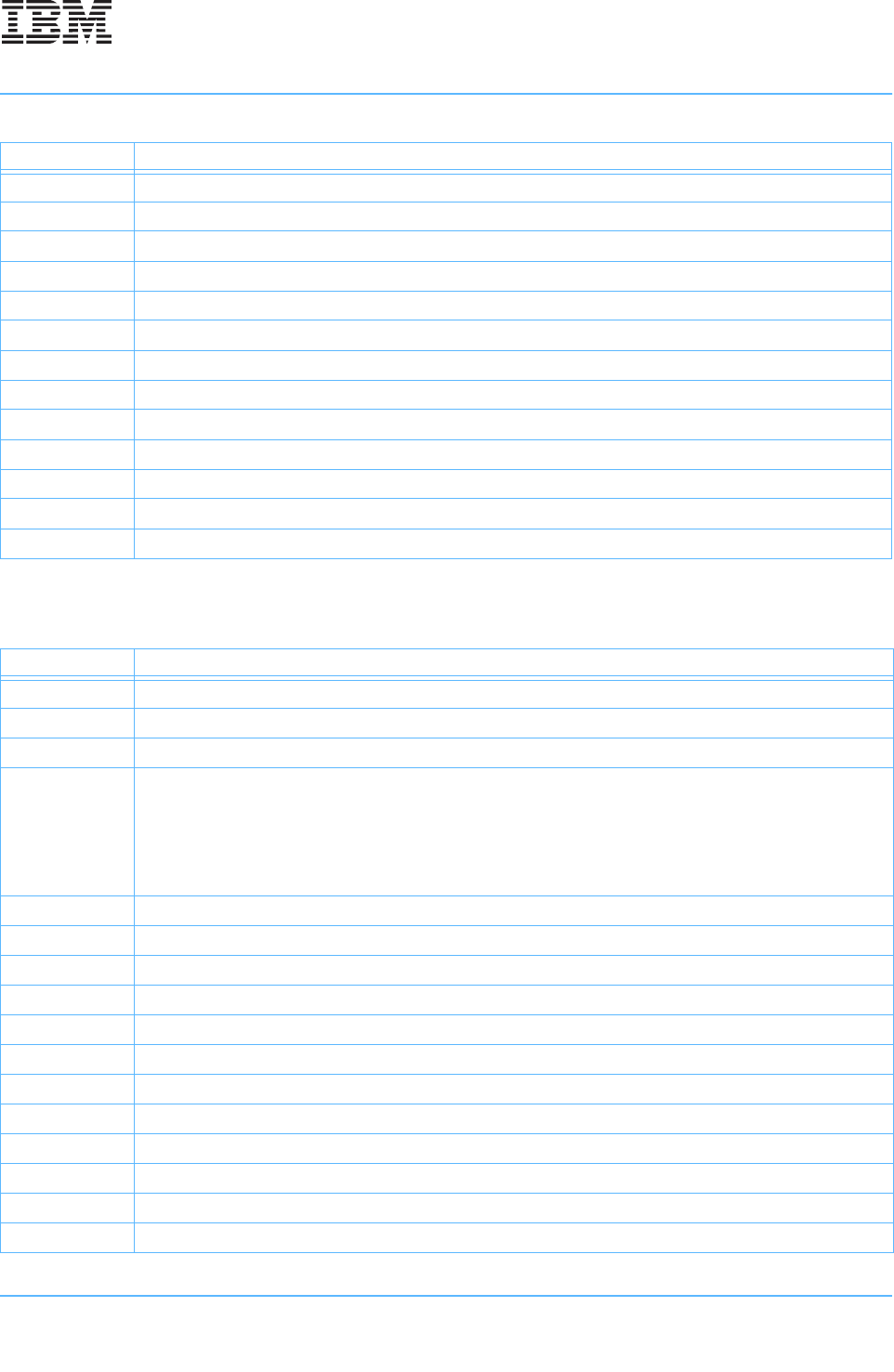

Bits MMCR1[0:4] specify events associated with PMC3, as shown in Table 11-4.

00 0101 Counts L1 instruction-cache misses.

00 0110 Counts ITLB misses.

00 0111 Counts L2 instruction misses.

00 1000 Counts branches predicted or resolved not taken.

00 1001 Reserved

00 1010 Counts times a reserved load operations completes.

00 1011 Counts completed load-and-store instructions.

00 1100 Counts snoops to the L1 and the L2.

001101 Counts the L1 castout to the L2.

001110 Counts completed system unit instructions.

001111 Counts instruction fetch misses in the L1.

010000 Counts branches allowing out-of-order execution that resolved correctly.

All others Reserved.

Table 11-4. PMC3 Events—MMCR1[0:4] Select Encodings (Page 1 of 2)

Encoding Description

0 0000 Register holds current value.

0 0001 Number of processor cycles.

0 0010 Number of completed instructions, not including folded branches.

0 0011

Number of transitions from 0 to 1 of specified bits in the Time Base Lower (TBL) register. Bits are specified through

RTCSELECT (MMCR0[7–8]).

00 47

01 51

10 55

11 63

0 0100 Number of instructions dispatched. 0, 1, or 2 per cycle.

0 0101 Number of L1 data-cache misses. Does not include cache operations.

0 0110 Number of data TLB (DTLB) misses.

0 0111 Number of L2 data misses.

0 1000 Number of predicted branches that were taken.

0 1001 Reserved.

0 1010 Number of store conditional instructions completed.

0 1011 Number of instructions completed from the floating-point unit (FPU).

0 1100 Number of L2 castouts caused by snoops to modified lines.

0 1101 Number of cache operations that hit in the L2 cache.

0 1110 Reserved.

0 1111 Number of cycles generated by L1 load misses.

Table 11-3. PMC2 Events—MMCR0[26:31] Select Encodings (Page 2 of 2)

Encoding Description