User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

Exceptions

Page 176 of 377

gx_04.fm.(1.2)

March 27, 2006

4.5.19 Exception Latencies

Latencies for taking various exceptions are variable based on the state of the machine when conditions to

produce an exception occur. The shortest latency possible is one cycle. In this case, an exception is signaled

in the cycle following the appearance of the conditions that generated that exception. In most cases, a hard

reset or machine check has a single-cycle latency to exception. The only situation that can prevent this is

when a speculative instruction is the next to complete. This case, which produces an extra 2-cycle minimum,

3-cycle maximum delay, only occurs if the branch guess that forced this instruction to be speculative was

resolved to be incorrect.

Another latency variable is introduced for a soft reset exception–recoverability. The time to reach a recover-

able state can depend on the time needed to complete or to cause an exception to an instruction at the point

of completion, the time needed to drain the completed store queue, or the time waiting for a correct empty

state so that a valid exception prefix (IP) can be saved. For other externally-generated exceptions, a further

delay might be incurred waiting for another exception, generated while reaching a recoverable state, to be

serviced.

Further delays are possible for other types of exceptions depending on the number and type of instructions

that must be completed before that exception can be serviced. See Section 4.5.20, Summary of Front-End

Exception Handling, to determine possible maximum latencies for different exceptions.

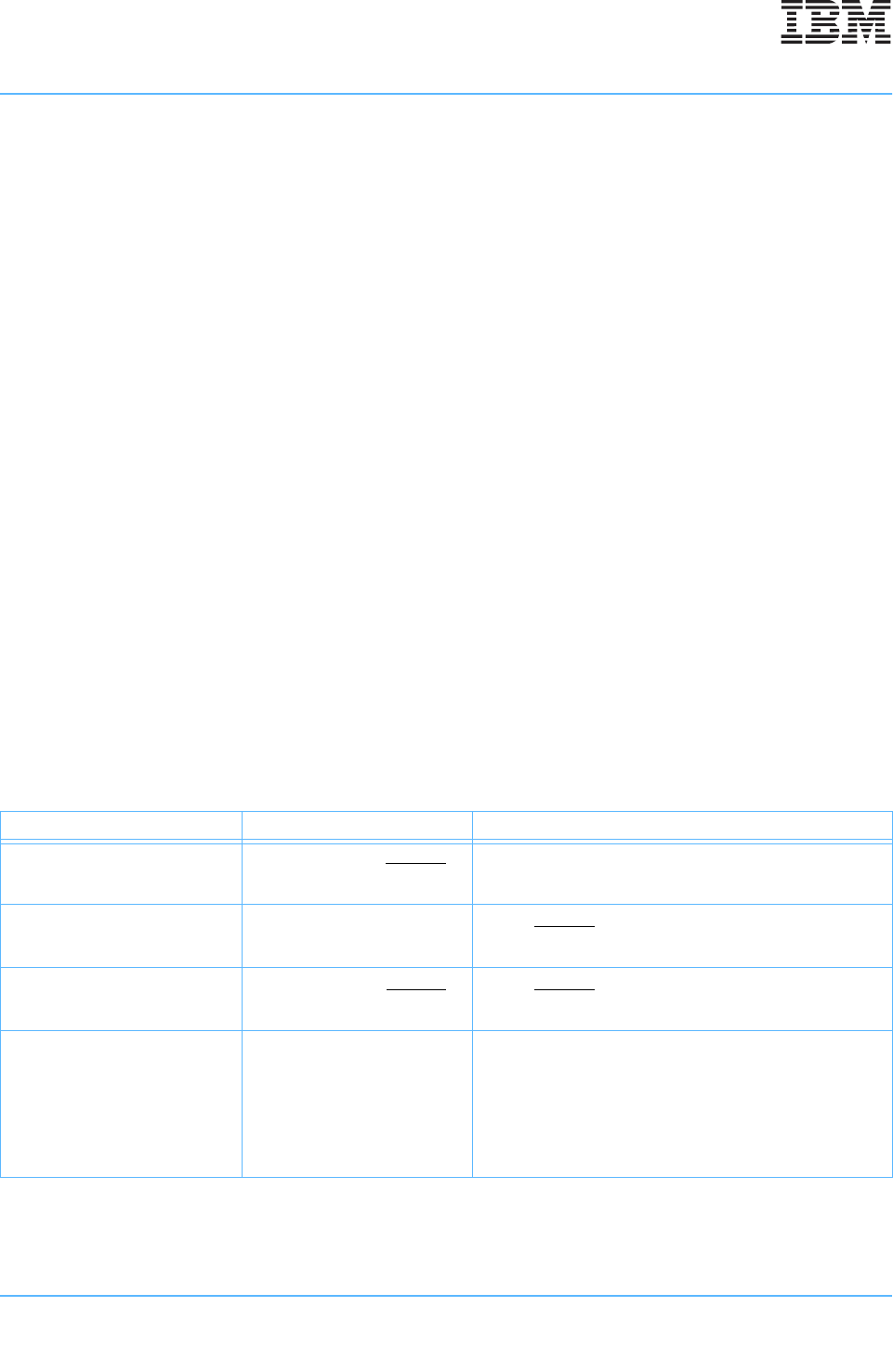

4.5.20 Summary of Front-End Exception Handling

Table 4-14 describes how the 750GX handles exceptions up to the point of signaling the appropriate excep-

tion to occur. Note that a recoverable state is reached in the 750GX if the completed store queue is empty

(drained, not canceled), and the instruction that is next in the program order has been signaled to complete

and has completed. If MSR[RI] = 0, the 750GX is in a nonrecoverable state by default. Also, completion of an

instruction is defined as performing all architectural register writes associated with that instruction, and then

removing that instruction from the completion buffer queue.

Table 4-14. Front-End Exception Handling Summary

(Page 1 of 2)

Exception Type Specific Exception Description

Asynchronous Nonmaskable

Nonrecoverable

System Reset for HRESET

Has highest priority and is taken immediately regardless of

other pending exceptions or recoverability. A nonspeculative

address is guaranteed.

Asynchronous Maskable

Nonrecoverable

Machine Check

Takes priority over any other pending exception except system

reset for HRESET

or POR. Taken immediately, regardless of

recoverability. A nonspeculative address is guaranteed.

Asynchronous Nonmaskable

Recoverable

System Reset for SRESET

Takes priority over any other pending exception except system

reset for HRESET

or POR or machine check. Taken immedi-

ately when a recoverable state is reached.

Asynchronous Maskable

Recoverable

SMI, EI, DEC

Before handling this type of exception, the next instruction in

program order must complete or cause an exception. If this

action causes another type of exception, that exception is

taken and the asynchronous maskable recoverable (AMR)

exception remains pending. Once an instruction is able to com-

plete without causing an exception, while the AMR exception is

enabled, further instruction completion is halted. The AMR

exception is then taken once a recoverable state is reached.