User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 94 of 377

gx_02.fm.(1.2)

March 27, 2006

Integer Logical Instructions

The logical instructions shown in Table 2-9 on page 94 perform bit-parallel operations on the specified oper-

ands. Logical instructions with CR updating enabled (uses dot suffix) and the AND Immediate (andi.) and

AND Immediate Shifted (andis.) instructions set the CR[CR0] field to characterize the result of the logical

operation. Logical instructions do not affect XER[SO], XER[OV], or XER[CA].

See Appendix F, “Simplified Mnemonics,” in the PowerPC Microprocessor Family: The Programming Envi-

ronments Manual for simplified mnemonic examples for integer logical operations.

Integer Rotate Instructions

Rotation operations are performed on data from a GPR, and the result, or a portion of the result, is returned to

a GPR. See Appendix F, “Simplified Mnemonics,” in the PowerPC Microprocessor Family: The Programming

Environments Manual for a complete list of simplified mnemonics that allows simpler coding of often-used

functions such as clearing the leftmost or rightmost bits of a register, left justifying or right justifying an arbi-

trary field, and simple rotates and shifts.

Integer rotate instructions rotate the contents of a register. The result of the rotation is either inserted into the

target register under control of a mask (if a mask bit is 1, the associated bit of the rotated data is placed into

the target register, and if the mask bit is 0, the associated bit in the target register is unchanged), or ANDed

with a mask before being placed into the target register.

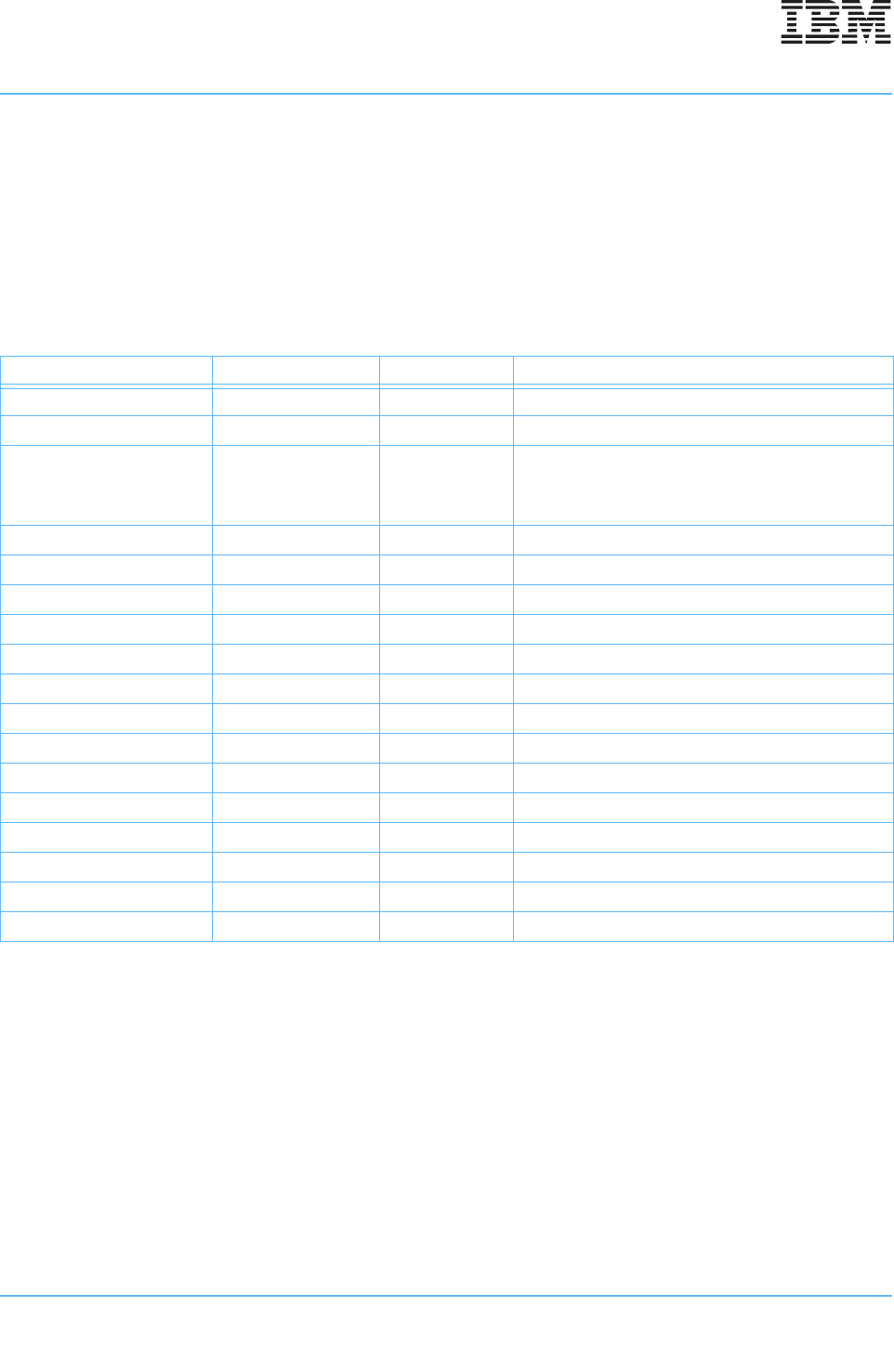

Table 2-9. Integer Logical Instructions

Name Mnemonic Syntax Implementation Notes

AND Immediate andi. rA,rS,UIMM —

AND Immediate Shifted andis. rA,rS,UIMM —

OR Immediate ori rA,rS,UIMM

The PowerPC Architecture defines ori r0,r0,0 as the pre-

ferred form for the no-op instruction. The dispatcher dis-

cards this instruction (except for pending trace or

breakpoint exceptions).

OR Immediate Shifted oris rA,rS,UIMM —

XOR Immediate xori rA,rS,UIMM —

XOR Immediate Shifted xoris rA,rS,UIMM —

AND and (and.) rA,rS,rB—

OR or (or.) rA,rS,rB—

XOR xor (xor.) rA,rS,rB—

NAND nand (nand.) rA,rS,rB—

NOR nor (nor.) rA,rS,rB—

Equivalent

eqv (eqv.) rA,rS,rB—

AND with Complement andc (andc.) rA,rS,rB—

OR with Complement orc (orc.) rA,rS,rB—

Extend Sign Byte extsb (extsb.) rA,rS—

Extend Sign Half Word extsh (extsh.) rA,rS—

Count Leading Zeros Word cntlzw (cntlzw.) rA,rS—