User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Bus Interface Operation

Page 294 of 377

gx_08.fm.(1.2)

March 27, 2006

8.3.2.1 Address-Bus Parity

The 750GX always generates 1 bit of correct odd-byte parity for each of the 4 bytes of address when a valid

address is on the bus. The calculated values are placed on the AP[0–3] outputs when the 750GX is the

address-bus master. If the 750GX is not the master and TS

and GBL are asserted together (qualified condi-

tion for snooping memory operations), the calculated values are compared with the AP[0–3] inputs. If there is

an error, and address-parity checking is enabled (HID0[EBA] set to 1), a machine-check exception is gener-

ated. An address-bus parity error causes a checkstop condition if MSR[ME] is cleared to 0. For more informa-

tion about checkstop conditions, see Chapter 4, Exceptions, on page 151.

8.3.2.2 Address Transfer Attribute Signals

The transfer attribute signals include several encoded signals such as the transfer type (TT[0–4]) signals,

transfer burst (TBST

) signal, transfer size (TSIZ[0–2]) signals, write-through (WT), and cache inhibit (CI).

Section 7.2.4, Address Transfer Attribute Signals, on page 255 describes the encodings for the address

transfer attribute signals.

Transfer Type (TT[0–4]) Signals

Snooping logic should fully decode the transfer type signals if the GBL

signal is asserted. Slave devices can

sometimes use the individual transfer type signals without fully decoding the group. For a complete descrip-

tion of the encoding for TT[0–4], see Table 8-1 and Table 8-2 on page 295.

Transfer Size (TSIZ[0–2]) Signals

The TSIZ[0–2] signals indicate the size of the requested data transfer as shown in Table 8-1. The TSIZ[0–2]

signals can be used along with TBST

and A[29–31] to determine which portion of the data bus contains valid

data for a write transaction or which portion of the bus should contain valid data for a read transaction. Note

that, for a burst transaction (as indicated by the assertion of TBST

), TSIZ[0–2] are always set to 0b010.

Therefore, if the TBST

signal is asserted, the memory system should transfer a total of eight words (32

bytes), regardless of the TSIZ[0–2] encodings.

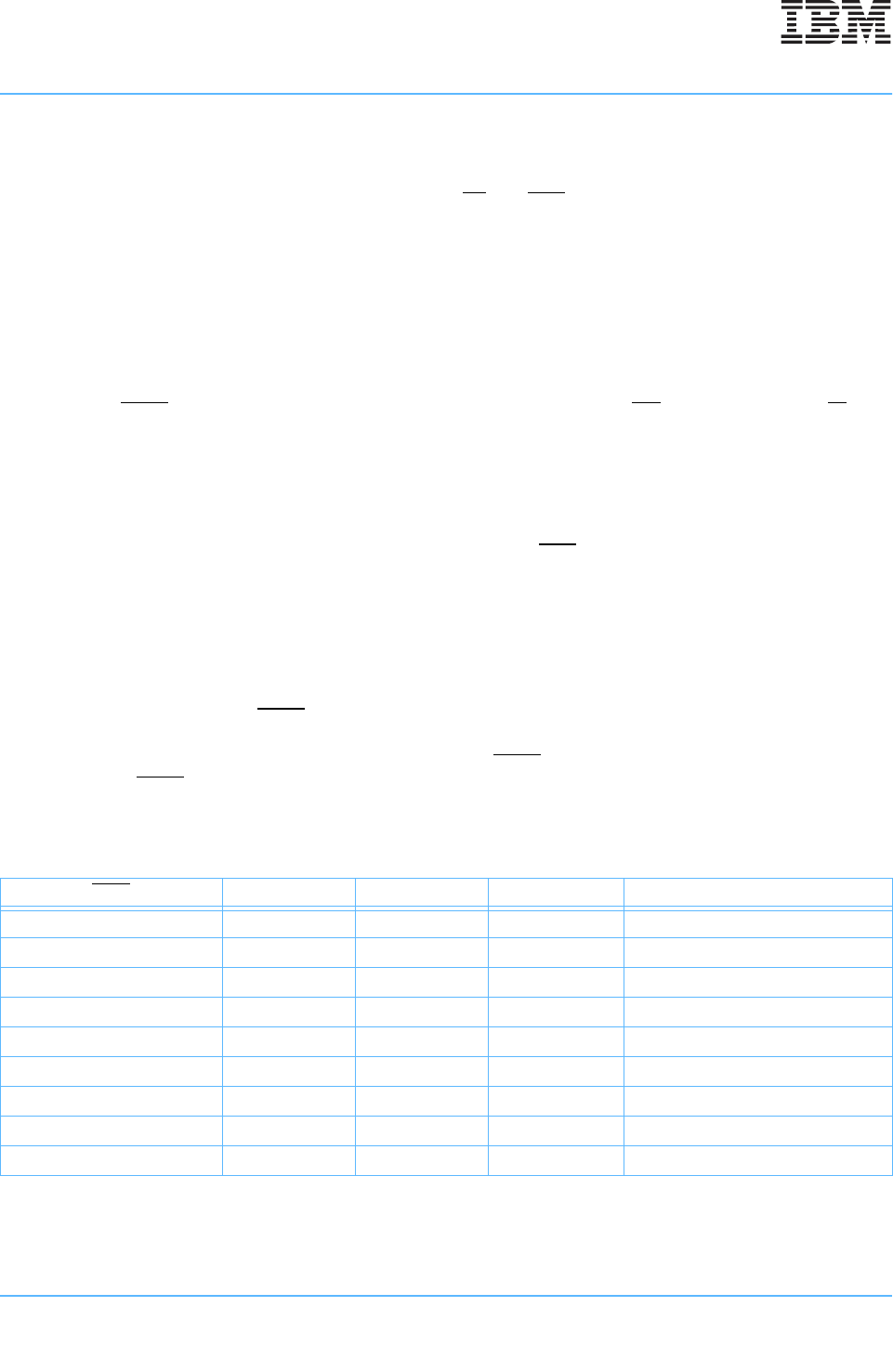

Table 8-1. Transfer Size Signal Encodings

TBST TSIZ0 TSIZ1 TSIZ2 Transfer Size

Asserted 0 1 0 8-word burst

Negated 0 0 0 8 bytes

Negated 0 0 1 1 byte

Negated 0 1 0 2 bytes

Negated 0 1 1 3 bytes

Negated 1 0 0 4 bytes

Negated 1 0 1 5 bytes (N/A)

Negated 1 1 0 6 bytes (N/A)

Negated 1 1 1 7 bytes (N/A)