User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Programming Model

Page 84 of 377

gx_02.fm.(1.2)

March 27, 2006

2.2.3.3 Time-Critical Floating-Point Operation

For time-critical applications where deterministic floating-point performance is required, the FPSCR bits must

be set with: the non-IEEE mode enabled, the floating-point exception masked, and all sticky bits set to one.

With these settings, the 750GX will not cause exceptions nor generate denormalized numbers, either of

which slows performance.

2.2.3.4 Floating-Point Storage Access Alignment

The 750GX does not provide hardware support for floating-point storage that is not word aligned. In these

cases, the 750GX invokes an alignment exception, and it is left up to software to break up the offending

storage access operation appropriately. In addition, some non-double-word-aligned storage accesses will

suffer a performance degradation as compared to an aligned access of the same type.

In general, floating-point single-word accesses should always be word aligned and floating-point double-word

accesses should always be double-word aligned. The frequent use of misaligned accesses is discouraged

since they can compromise the overall performance of the processor.

2.2.3.5 Optional Floating-Point Graphics Instructions

The 750GX implements the graphics instructions Store Floating-Point as Integer Word Indexed (stfiwx),

Floating Select fsel(.), fres(.), and frsqrte(.). For Floating Reciprocal Estimate Single A-Form (fres), the esti-

mate is 12 bits of precision. For Floating Reciprocal Square-root Estimate A-Form (frsqrte), the estimate is

12 bits of precision with the remaining bits zero.

.

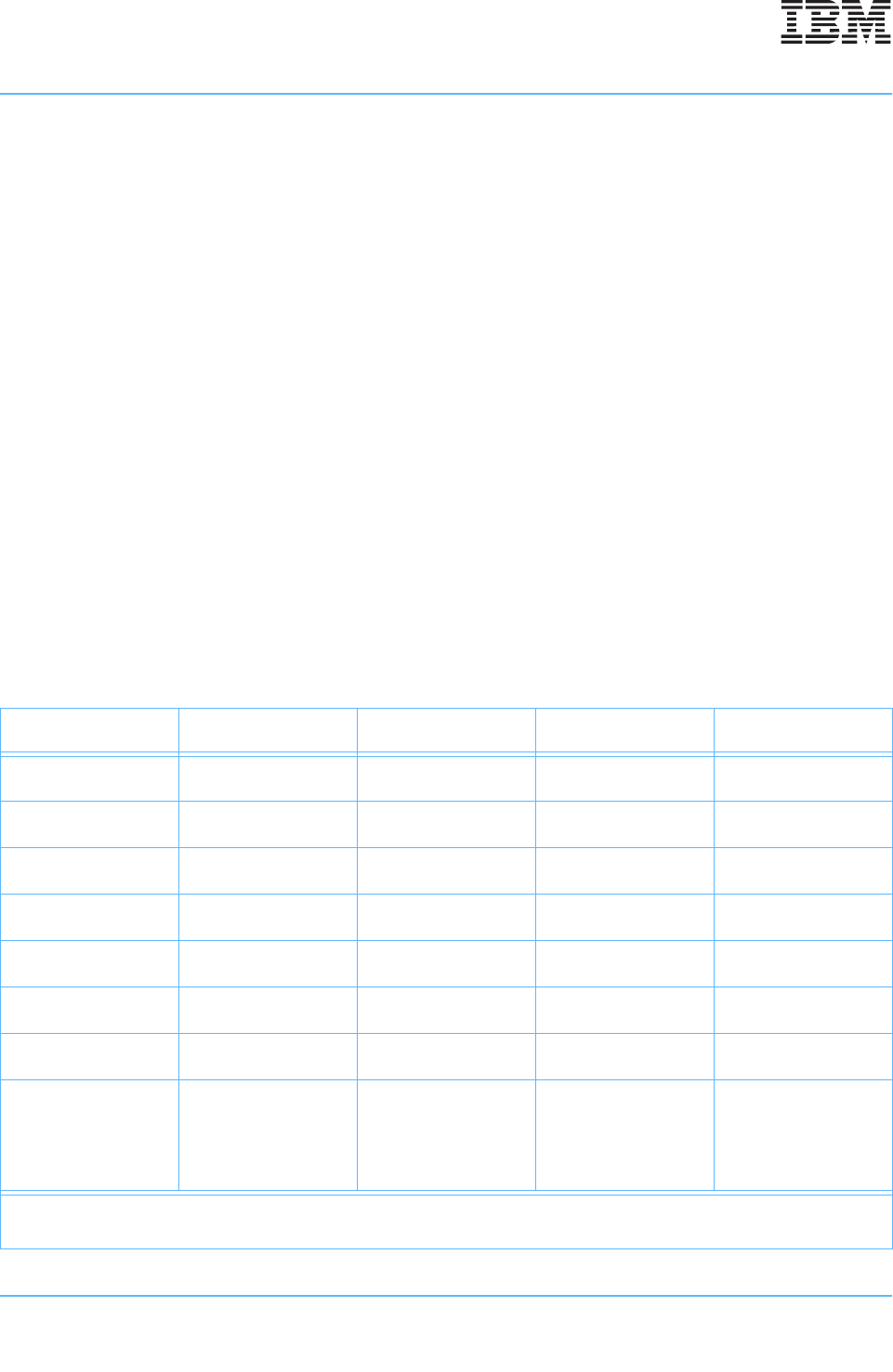

Table 2-5. Floating-Point Operand Data-Type Behavior (Page 1 of 2)

Operand A

Data Type

Operand B

Data Type

Operand C

Data Type

IEEE Mode

(NI = 0)

Non-IEEE Mode

(NI = 1)

Single denormalized

Double denormalized

Single denormalized

Double denormalized

Single denormalized

Double denormalized

Normalize all three Zero all three

Single denormalized

Double denormalized

Single denormalized

Double denormalized

Normalized or zero Normalize A and B Zero A and B

Normalized or zero

Single denormalized

Double denormalized

Single denormalized

Double denormalized

Normalize B and C Zero B and C

Single denormalized

Double denormalized

Normalized or zero

Single denormalized

Double denormalized

Normalize A and C Zero A and C

Single denormalized

Double denormalized

Normalized or zero Normalized or zero Normalize A Zero A

Normalized or zero

Single denormalized

Double denormalized

Normalized or zero Normalize B Zero B

Normalized or zero Normalized or zero

Single denormalized

Double denormalized

Normalize C Zero C

Single quiet not-a-number

(QNaN)

Single signaling not-a-

number (SNaN)

Double QNaN

Double SNaN

Don’t care Don’t care QNaN

1

QNaN

1

1. Prioritize according to Chapter 3, “Operand Conventions,” in the PowerPC Microprocessor Family: The Programming Environ-

ments Manual.