User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_05.fm.(1.2)

March 27, 2006

Memory Management

Page 189 of 377

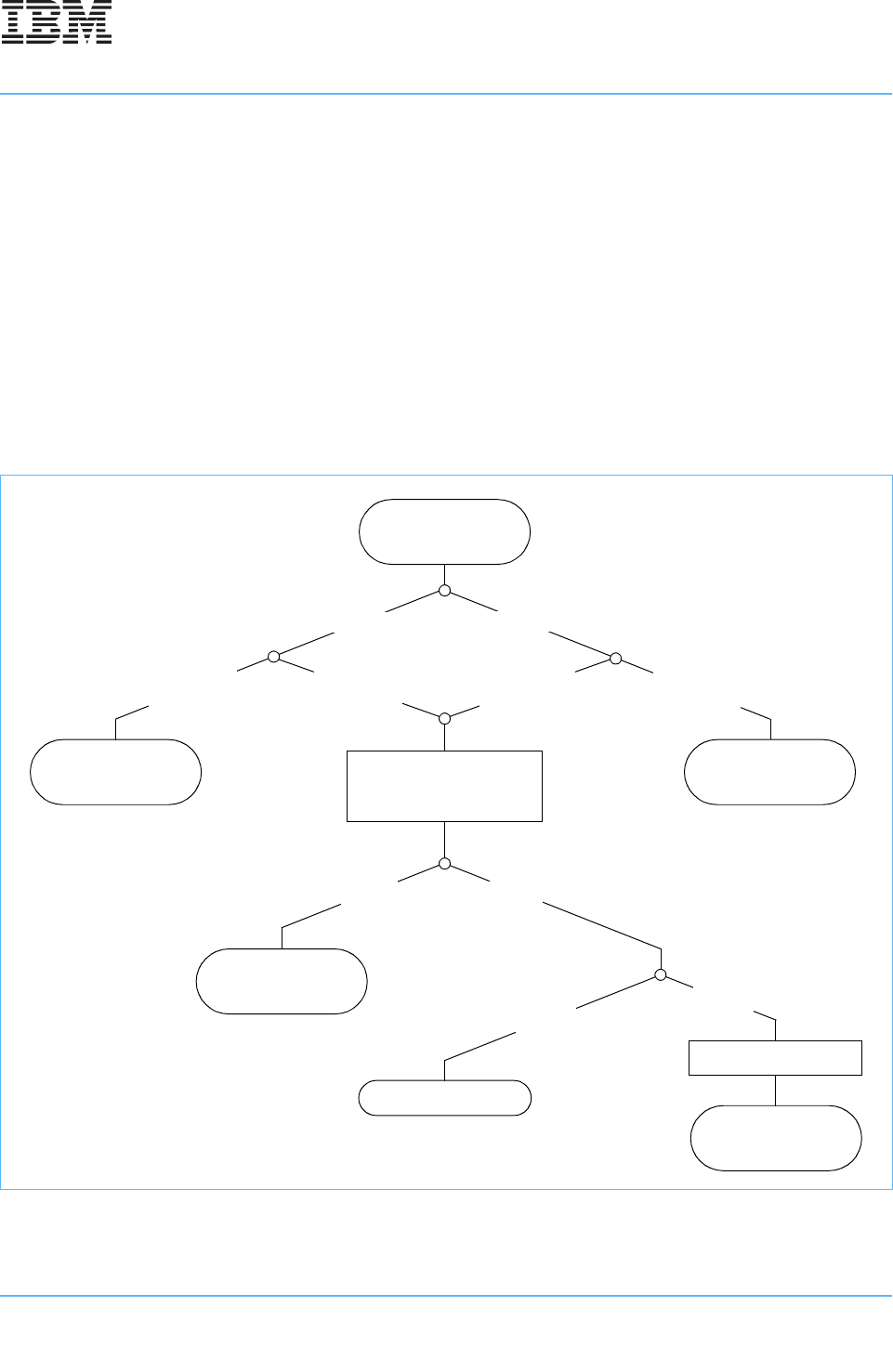

5.1.6 General Flow of MMU Address Translation

The following sections describe the general flow used by PowerPC processors to translate effective

addresses to virtual and then physical addresses.

5.1.6.1 Real-Addressing Mode and Block-Address-Translation Selection

When an instruction or data access is generated and the corresponding instruction or data translation is

disabled (MSR[IR] = 0 or MSR[DR] = 0), then the real-addressing mode is used (physical address equals

effective address), and the access continues to the memory subsystem as described in Section 5.2, Real-

Addressing Mode, on page 195.

Figure 5-5 shows the flow the MMUs use in determining whether to select real-addressing mode, block-

address translation, or the segment descriptor to select page-address translation.

Note: If the BAT array search results in a hit, then the access is qualified with the appropriate protection bits.

If the access violates the protection mechanism, then an exception (either ISI or DSI) is generated.

Figure 5-5. General Flow of Address Translation (Real-Addressing Mode and Block)

Perform Address

Translation with

Segment Descriptor

Access Faulted

Compare Address with

Instruction or Data BAT

Array (As Appropriate)

Translate Address

Perform Real

Addressing Mode

Translation

Effective Address

Generated

Continue Access

to Memory

Subsystem

(See The Programming

Environments Manual)

(See Figure 5-6 on

page 191)

Instruction

Translation Disabled

(MSR[IR] = 0)

BAT

Array

Miss

Instruction Access

Access

Protected

Access

Permitted

Instruction

Translation Enabled

(MSR[IR] = 1)

Data

Translation Enabled

(MSR[DR] = 1)

Data

Translation Disabled

(MSR[DR] = 0)

Data Access

BAT

Array

Hit

Perform Real

Addressing Mode

Translation