User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_11.fm.(1.2)

March 27, 2006

Performance Monitor and System Related Features

Page 361 of 377

11.9 Checkstops

A checkstop causes the processor to halt and assert the checkstop output pin, CKSTP_OUT. Once the

750GX enters a checkstop state, only a hard reset can clear the processor.

11.9.1 Checkstop Sources

Following is the list of checkstop sources:

• Machine Check with MSR[ME] = 0.

If MSR[ME] = 0 when a machine-check interrupt occurs, then the checkstop state is entered. The

machine-check sources for the 750GX are as follows:

–TEA

assertion on the 60x bus

– Address-parity error on the 60x bus

– Data-parity error on the 60x bus

– Machine-check input pin (MCP

)

– Locked L2 Snoop, with the snoop hit in locked line error enable bit in the L2 Cache Control Register

(L2CR[SHEE]) set

– A parity error in either the instruction tag, data tag, instruction cache, data cache, or L2 tag (if

enabled)

• Checkstop input pin (CKSTP_IN

)

11.9.2 Checkstop Control Bits

Some of the checkstop sources can be controlled via Hardware-Implementation-Dependent Register 0

(HID0) and the L2CR register bits.

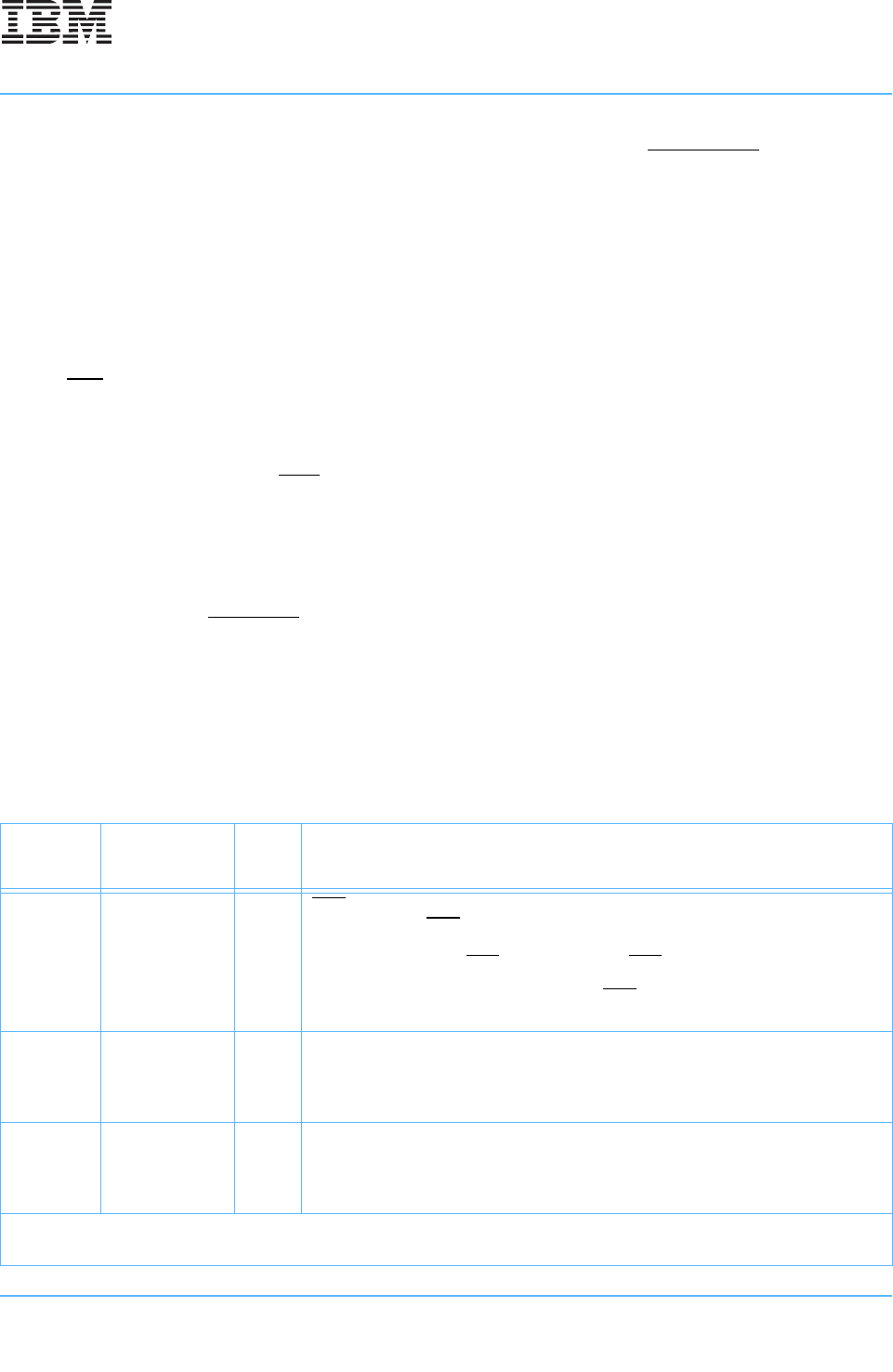

Table 11-6. HID0 Checkstop Control Bits

Bits Field Name

Hard

Reset

State

Description

0EMCP0

MCP

pin mask bit

1 Enables MCP

to cause a checkstop if MSR(ME) = 0, or a machine-check inter-

rupt if MSR(ME) = 1.

0 Masks out the MCP

pin. Therefore, the MCP pin cannot generate a machine-

check interrupt or a checkstop. The main purpose of this bit is to mask out fur-

ther machine-check interrupts from MCP

, similar to the MSR(EE) bit for exter-

nal interrupts.

2EBA0

Bus address-parity checking enable

1 Enables an address-parity error to cause a checkstop if MSR(ME) = 0, or a

machine-check interrupt if MSR(ME) = 1.

0 Prevents address-parity checking.

3EBD0

Bus data-parity checking enable

1 Enables a data-parity error to cause a checkstop if MSR(ME) = 0, or a

machine-check interrupt if MSR(ME) = 1.

0 Prevents data-parity checking.

Note: The EBA and EBD bits allow the processor to operate with memory subsystems that do not generate parity. A checkstop latch

is provided in the COP to indicate the checkstop source.