User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

gx_04.fm.(1.2)

March 27, 2006

Exceptions

Page 177 of 377

4.5.21 Timer Facilities

At power-on reset (POR), the 750GX initializes the Time Base and Decrementer Registers to the following

values:

• Time Base Upper Register (TBU) = 0x00000000

• Time Base Lower Register (TBL) = 0x00000000

• Decrementer Register (DEC) = 0xFFFFFFFF

4.5.22 External Access Instructions

The 750GX implements the eciwx and ecowx instructions. Executing these instructions while MSR[DR] = 0

is considered a programming error, and the physical address on the bus is undefined. Executing these

instructions to a direct-store (T = 1) segment causes a data-storage exception (DSI).

The 750GX implements the External Access Register (EAR) to support the external access instructions. Bit 0

implements the Enable bit. Bits 1 to 25 are reserved. Bits 26 and 27 are not implemented and are reserved.

Bits 28 to 31 are the implemented bits of the Resource ID (RID).

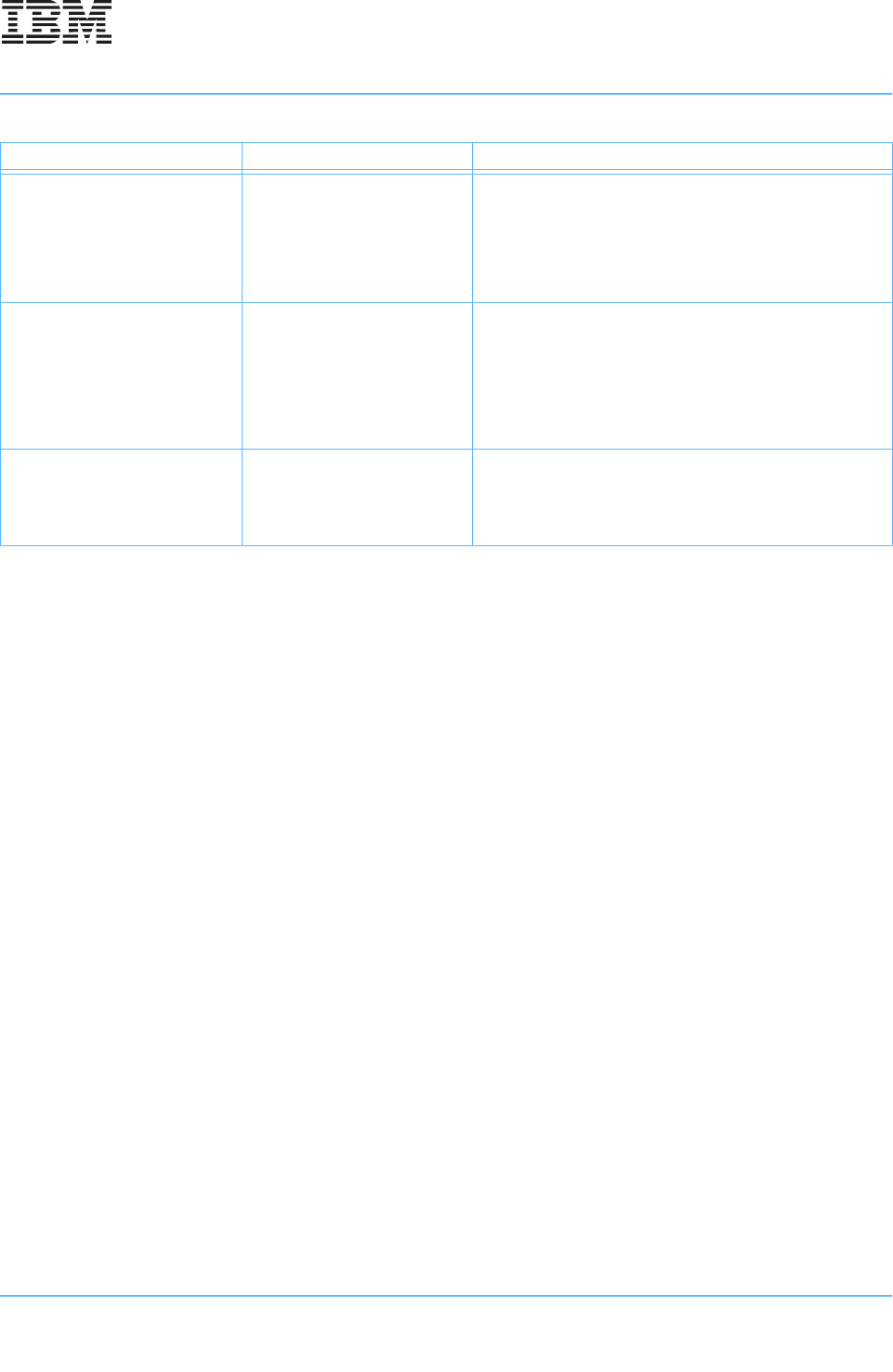

Instruction Fetch ISI

Once this type of exception is detected, dispatch is halted and

the current instruction stream is allowed to drain out of the

machine. If completing any of the instructions in this stream

causes an exception, that exception is taken and the instruc-

tion fetch exception is forgotten. Otherwise, once the machine

is empty and a recoverable state is reached, the instruction

fetch exception is taken.

Instruction Dispatch/Execution

Program, DSI, Alignment, FPA,

SC, IABR, DABR

This type of exception is determined at dispatch or execution of

an instruction. The exception remains pending until all instruc-

tions in program order before the exception-causing instruction

are completed. The exception is then taken without completing

the exception-causing instruction. If any other exception condi-

tion is created in completing these previous instructions in the

machine, that exception takes priority over the pending Instruc-

tion Dispatch/Execution exception, which is then forgotten.

Post Instruction Execution Trace

This type of exception is generated following execution and

completion of an instruction while a trace mode is enabled. If

executing the instruction produces conditions for another type

of exception, that exception is taken and the Post Instruction

Execution exception is forgotten for that instruction.

Table 4-14. Front-End Exception Handling Summary (Page 2 of 2)

Exception Type Specific Exception Description