User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

gx_04.fm.(1.2)

March 27, 2006

Exceptions

Page 167 of 377

The following is also true after a hard reset operation:

• External checkstops are enabled.

• The on-chip test interface has given control of the I/Os to the rest of the chip for functional use.

• Since the reset exception has data and instruction translation disabled (MSR[DR] and MSR[IR] both

cleared), the chip operates in direct address-translation mode (referred to as the real-addressing mode in

the architecture specification).

• Time from HRESET

deassertion until the 750GX asserts the first transfer start (TS) (bus parked on the

750GX) or BG

is 8 to 12 bus clocks (SYSCLK).

4.5.2 Machine-Check Exception (0x00200)

The 750GX implements the machine-check exception as defined in the PowerPC Architecture (OEA). It

conditionally initiates a machine-check exception after an address or data-parity error occurred on the bus or

in either the L1 or L2 cache, after receiving a qualified transfer error acknowledge (TEA

) indication on the

750GX bus, or after the machine-check interrupt (MCP

) signal had been asserted. As defined in the OEA, the

exception is not taken if MSR[ME] is cleared, in which case the processor enters the checkstop state.

Certain machine-check conditions can be enabled and disabled using HID0 bits, as described in Table 4-8.

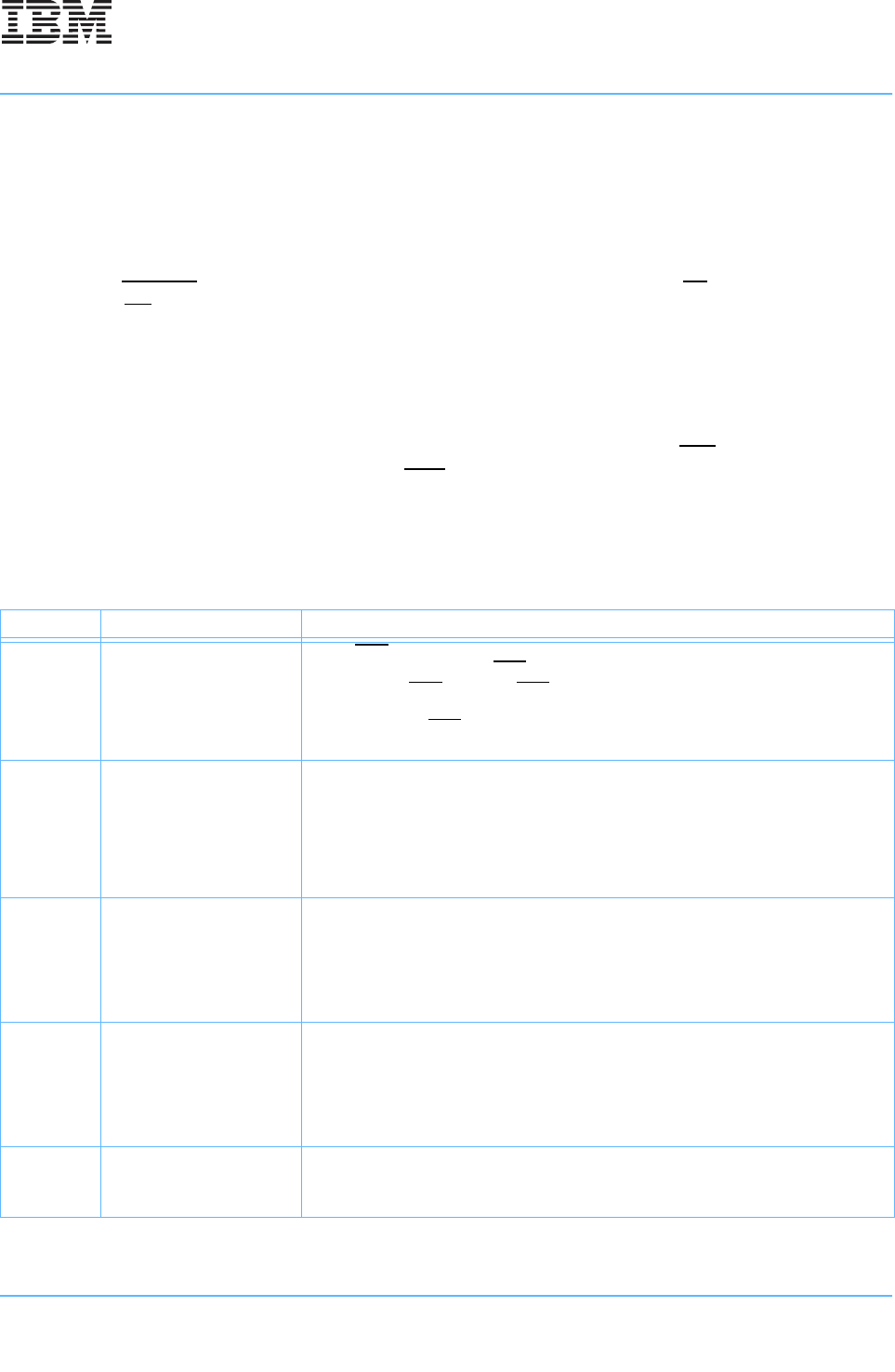

Table 4-8. HID0 Machine-Check Enable Bits

Bits Field Name Description

0EMCP

Enable MCP

. The primary purpose of this bit is to mask out further machine-check excep-

tions caused by assertion of MCP

, similar to how MSR[EE] can mask external interrupts.

0Masks MCP

. Asserting MCP does not generate a machine-check exception or a

checkstop.

1 Asserting MCP

causes a checkstop if MSR[ME] = 0 or a machine-check excep-

tion if MSR[ME] = 1.

1DBP

Disable 60x bus address-parity and data-parity generation.

0 Parity generation is enabled.

1 Disable parity generation. If the system does not use address or data parity and

the respective parity checking is disabled (HID0[EBA] or HID0[EBD] = 0), input

receivers for those signals are disabled, do not require pull-up resistors, and

therefore should be left unconnected. If all parity generation is disabled, all parity

checking should also be disabled and parity signals need not be connected.

2EBA

Enable/disable 60x bus address-parity checking.

0 Prevents address-parity checking.

1 Allows an address-parity error to cause a checkstop if MSR[ME] = 0 or a

machine-check exception if MSR[ME] = 1.

EBA and EBD allow the processor to operate with memory subsystems that do not gener-

ate parity.

3EBD

Enable 60x bus data-parity checking.

0 Parity checking is disabled.

1 Allows a data-parity error to cause a checkstop if MSR[ME] = 0 or a machine-

check exception if MSR[ME] = 1.

EBA and EBD allow the processor to operate with memory subsystems that do not gener-

ate parity.

15 NHR

Not hard reset (software use only)

0 A hard reset occurred if software previously set this bit

1 A hard reset has not occurred.