User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_08.fm.(1.2)

March 27, 2006

Bus Interface Operation

Page 301 of 377

address tenures occur until the current snoop push from the 750GX is completed. Snoop push delays can

also be avoided by operating the L2 cache in write-through mode so no snoop pushes are required by the L2

cache.

8.4 Data-Bus Tenure

This section describes the data-bus arbitration, transfer, and termination phases defined by the 750GX

memory-access protocol. The phases of the data tenure are identical to those of the address tenure, under-

scoring the symmetry in the control of the two buses.

8.4.1 Data-Bus Arbitration

Data-bus arbitration uses the data arbitration signal group—DBG

, DBWO, and DBB. Additionally, the combi-

nation of TS

and TT[0–4] provides information about the data-bus request to external logic.

The TS

signal is an implied data-bus request from the 750GX. The arbiter must qualify TS with the transfer

type (TT) encodings to determine if the current address transfer is an address-only operation, which does not

require a data-bus transfer (see Figure 8-9). If the data bus is needed, the arbiter grants data-bus mastership

by asserting the DBG

input to the 750GX. As with the address-bus arbitration phase, the 750GX must qualify

the DBG

input with a number of input signals before assuming bus mastership, as shown in Figure 8-10.

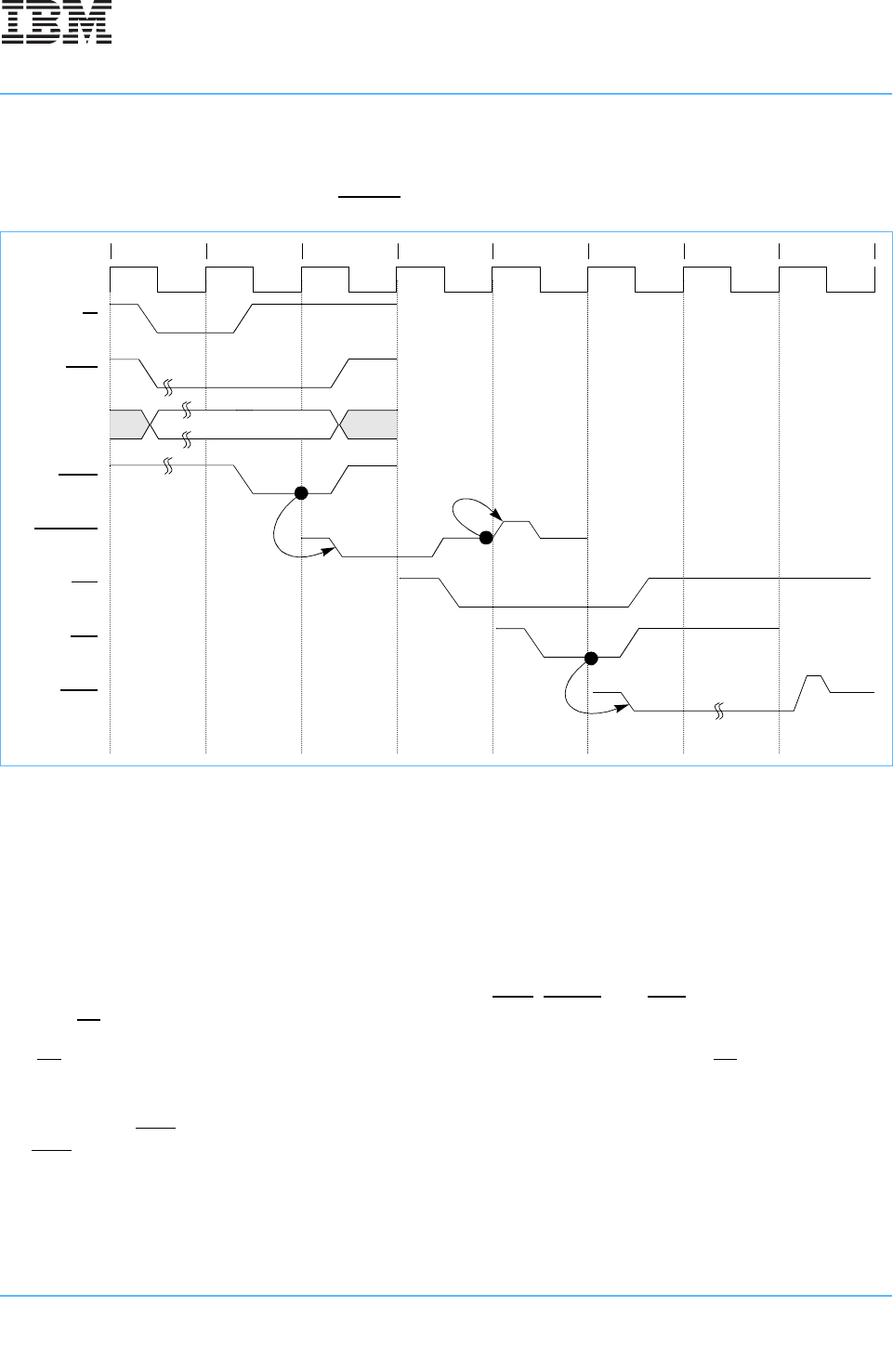

Figure 8-9. Snooped Address Cycle with ARTRY

12 34567

ts

abb

addr

aack

ARTRY

BR

qualBG

ABB

8