User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_05.fm.(1.2)

March 27, 2006

Memory Management

Page 197 of 377

page-address translation and not for translations made with the BAT mechanism or for accesses that corre-

spond to direct-store (T = 1) segments. Furthermore, R and C bits are maintained only for accesses made

while address translation is enabled (MSR[IR] = 1 or MSR[DR] = 1).

In the 750GX, the referenced and changed bits are updated as follows.

• For TLB hits, the C bit is updated according to Table 5-7.

• For TLB misses, when a table-search operation is in progress to locate a PTE, the R and C bits are

updated (set, if required) to reflect the status of the page based on this access.

Table 5-7 shows that the status of the C bit in the TLB entry (in the case of a TLB hit) is what causes the

processor to update the C bit in the PTE (the R bit is assumed to be set in the page tables if there is a TLB

hit). Therefore, when software clears the R and C bits in the page tables in memory, it must invalidate the TLB

entries associated with the pages whose referenced and changed bits were cleared.

The Data Cache Block Touch (dcbt) and Data Cache Block Touch for Store (dcbtst) instructions can execute

if there is a TLB or BAT hit or if the processor is in real-addressing mode. In the case of a TLB or BAT miss,

these instructions are treated as no-ops. They do not initiate a table-search operation, and they do not set

either the R or C bits.

As defined by the PowerPC Architecture, the referenced and changed bits are updated as if address transla-

tion were disabled (real-addressing mode). If these update accesses hit in the data cache, they are not seen

on the external bus. If they miss in the data cache, they are performed as typical cache-line-fill accesses on

the bus (assuming the data cache is enabled).

5.4.1.1 Referenced Bit

The referenced (R) bit of a page is located in the PTE in the page table. Every time a page is referenced (with

a read or write access) and the R bit is zero, the 750GX sets the R bit in the page table. The OEA specifies

that the referenced bit can be set immediately, or the setting can be delayed until the memory access is

determined to be successful. Because the reference to a page is what causes a PTE to be loaded into the

TLB, the referenced bit in all TLB entries is effectively always set. The processor never automatically clears

the referenced bit.

The referenced bit is only a hint to the operating system about the activity of a page. At times, the referenced

bit might be set although the access was not logically required by the program or even if the access was

prevented by memory protection. Examples of this in PowerPC systems include the following:

• Fetching of instructions not subsequently executed.

• A memory reference caused by a speculatively executed instruction that is mispredicted.

• Accesses generated by an lswx or stswx instruction with a zero length.

• Accesses generated by an stwcx. instruction when no store is performed because a reservation does not

exist.

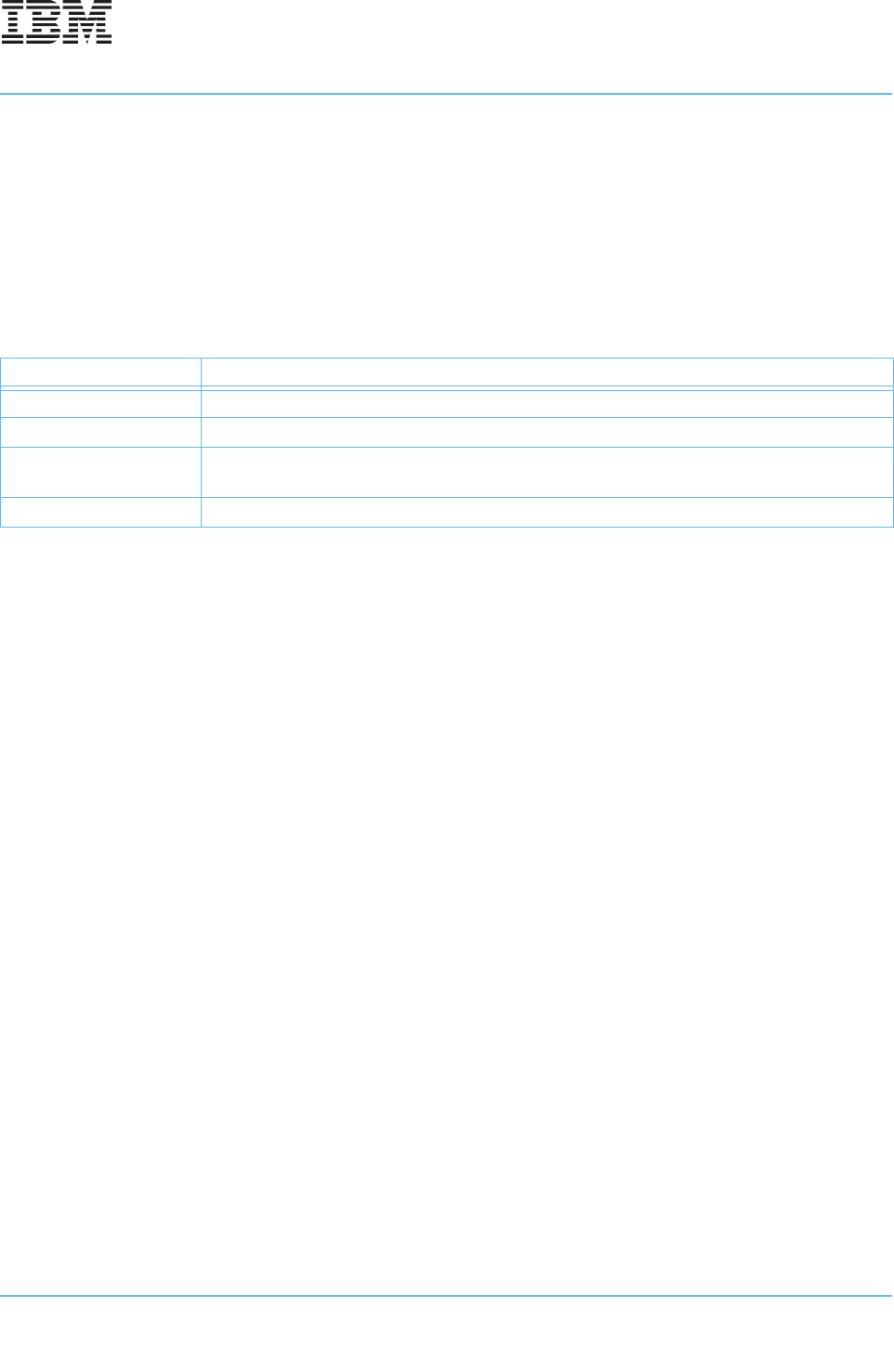

Table 5-7. Table-Search Operations to Update History Bits—TLB Hit Case

R and C bits in TLB Entry Processor Action

00 Combination does not occur

01 Combination does not occur

10

Read: No special action

Write: The 750GX initiates a table-search operation to update the C bit.

11 No special action for read or write