User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

gx_08.fm.(1.2)

March 27, 2006

Bus Interface Operation

Page 307 of 377

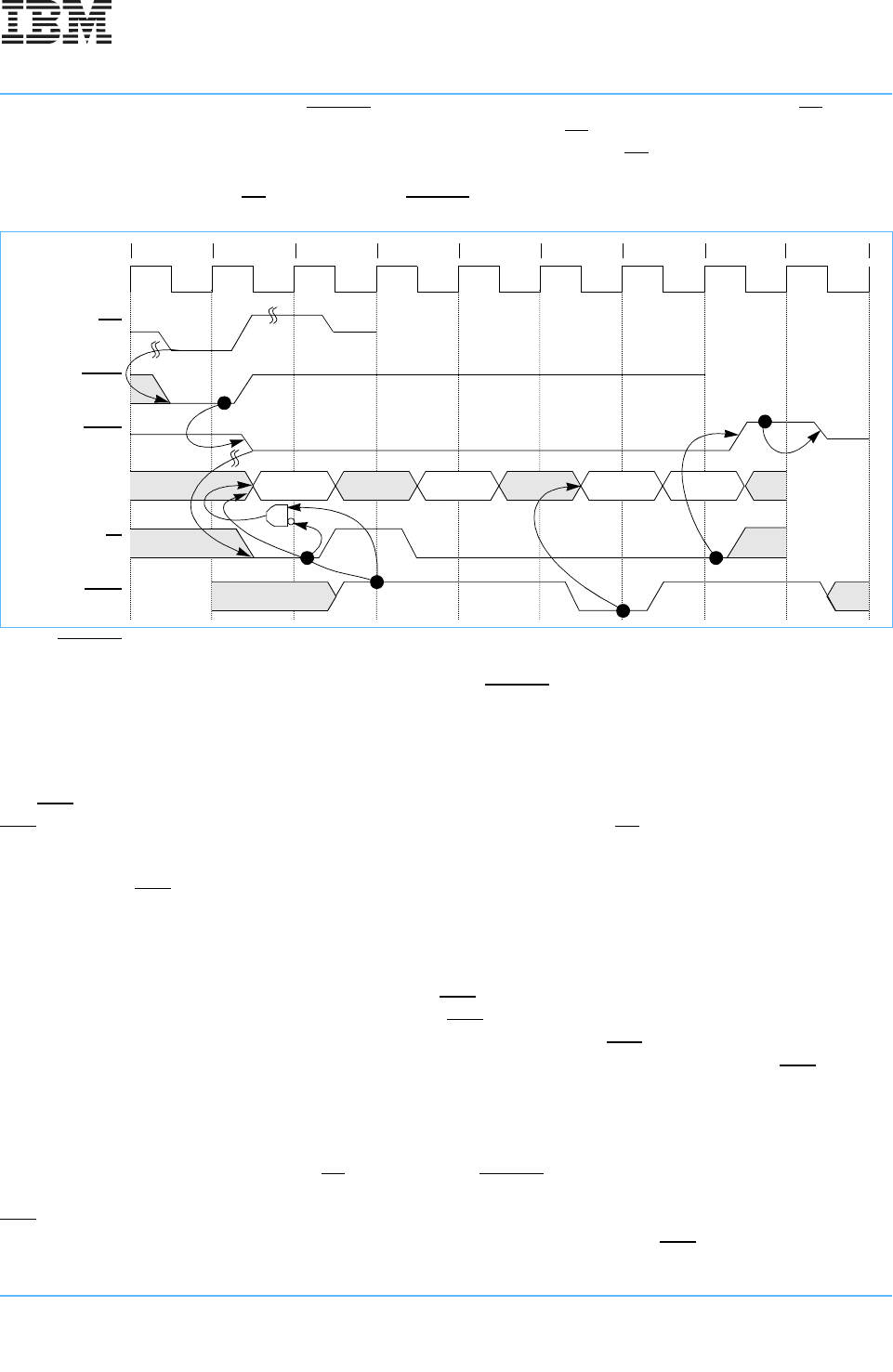

Figure 8-15 shows the effect of using DRTRY during a burst read. It also shows the effect of using TA to pace

the data-transfer rate. Notice that in bus clock cycle 3 of Figure 8-15, TA

is negated for the second data beat.

The 750GX data pipeline does not proceed until bus clock cycle 4 when the TA

is reasserted.

Note: D

RTRY is useful for systems that implement predicted forwarding of data such as those with direct-

mapped, third-level caches where hit or miss is determined on the following bus clock cycle, or for parity-

checked or ECC-checked memory systems. Also note that DRTRY

might not be implemented on other

PowerPC processors.

8.4.4.2 Data-Transfer Termination Due to a Bus Error

The TEA

signal indicates that a bus error occurred. It might be asserted during data-bus tenure. Asserting

TEA

to the 750GX terminates the transaction. That is, further assertions of TA are ignored and the data-bus

tenure is terminated.

Assertion of the TEA

signal causes a machine-check exception (and possibly a checkstop condition within

the 750GX).

Note: The 750GX does not implement a synchronous error capability for memory accesses. This means that

the exception instruction pointer saved into Machine Status Save/Restore Register 0 (SRR0) does not point

to the memory operation that caused the assertion of TEA

, but to the instruction about to be executed (per-

haps several instructions later). However, assertion of TEA

does not invalidate data entering the GPR or the

cache. Additionally, the address corresponding to the access that caused TEA

to be asserted is not latched

by the 750GX. To recover, the exception handler must determine and remedy the cause of the TEA

, or the

750GX must be reset. Therefore, this function should only be used to indicate fatal system conditions to the

processor.

After the 750GX has committed to run a transaction, that transaction must eventually complete. Address retry

causes the transaction to be restarted. T

A wait states and DRTRY assertion for reads delay termination of

individual data beats. Eventually, however, the system must either terminate the transaction or assert the

TEA

signal. For this reason, care must be taken to check for the end of physical memory and the location of

certain system facilities to avoid memory accesses that result in the assertion of TEA

.

Figure 8-15. Read Burst with TA

Wait States and DRTRY

TS

qual DBG

DBB

data

ta

drtry

123456789