User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Memory Management

Page 194 of 377

gx_05.fm.(1.2)

March 27, 2006

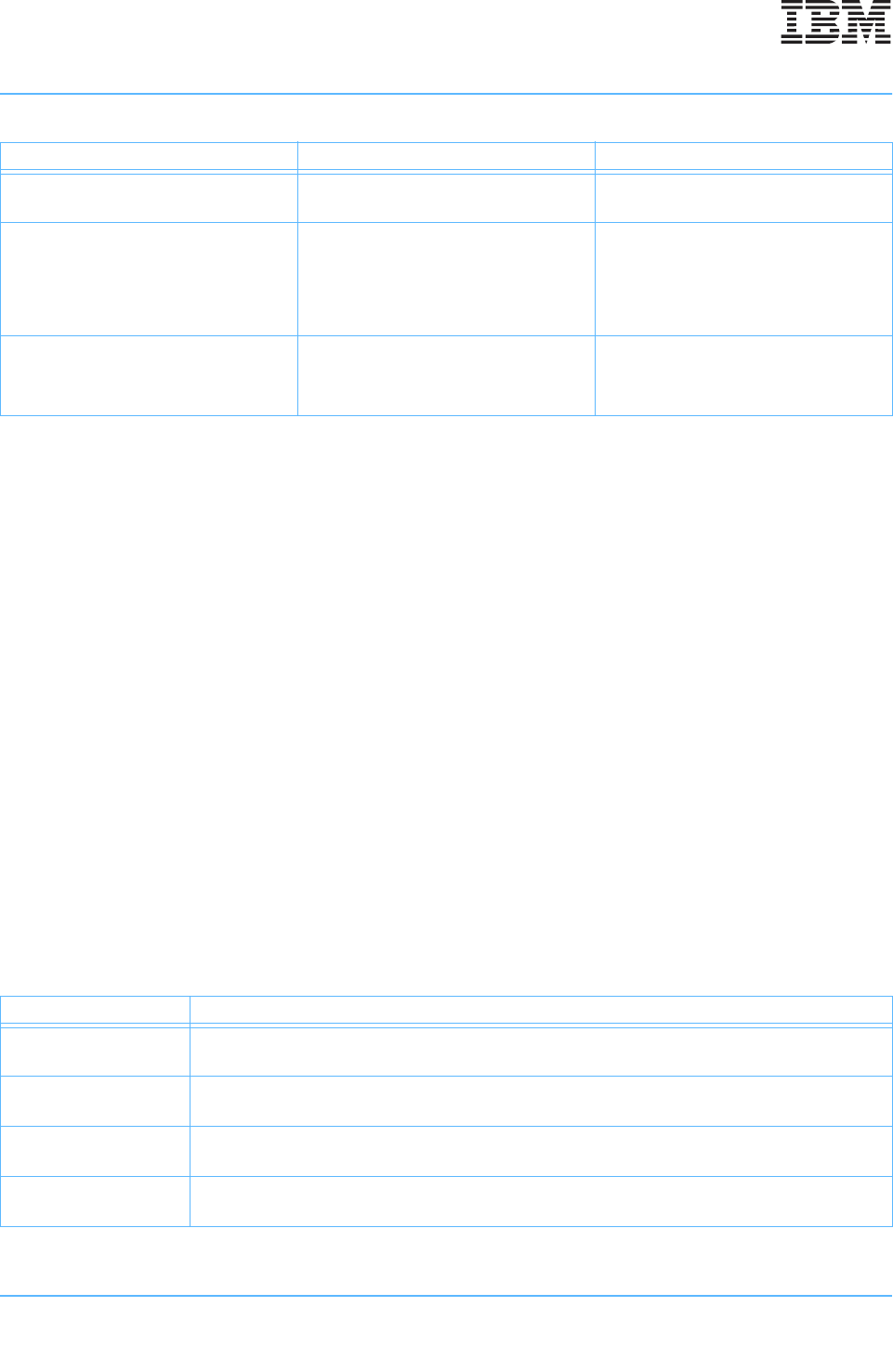

5.1.8 MMU Instructions and Register Summary

The MMU instructions and registers allow the operating system to set up the block-address-translation areas

and the page tables in memory.

Notes:

• Because the implementation of TLBs is optional, the instructions that refer to these structures are also

optional. However, as these structures serve as caches of the page table, the architecture specifies a

software protocol for maintaining coherency between these caches and the tables in memory whenever

the tables in memory are modified. When the tables in memory are changed, the operating system

purges these caches of the corresponding entries, allowing the translation caching mechanism to refetch

from the tables when the corresponding entries are required.

• Also note that the 750GX implements all TLB-related instructions except TLB Invalidate All (tlbia), which

is treated as an illegal instruction.

Because the MMU specification for PowerPC processors is so flexible, it is recommended that the software

that uses these instructions and registers be encapsulated into subroutines to minimize the impact of

migrating across the family of implementations.

Table 5-5 summarizes the 750GX’s instructions that specifically control the MMU. For more detailed informa-

tion about the instructions, see Chapter 2, Programming Model, on page 57 and Chapter 8, “Instruction Set,”

in the PowerPC Microprocessor Family: The Programming Environments Manual

.

eciwx or ecowx attempted when external

control facility disabled

eciwx or ecowx attempted with EAR[E] = 0

DSI exception

DSISR[11] = 1

Load Multiple Word (lmw), Store Multiple

Word (stmw), lswi, Load String Word

Immediate (lswx), Store String Word Imme-

diate (stswi), or Store String Word Indexed

x-form (stswx) instruction attempted in little-

endian mode

lmw, stmw, lswi, lswx, stswi, or stswx

instruction attempted while MSR[LE] = 1

Alignment exception

Operand misalignment

Translation enabled and a floating-point

load/store, stmw, stwcx., lmw, lwarx,

eciwx, or ecowx instruction operand is not

word-aligned

Alignment exception (some of these cases

are implementation-specific)

Table 5-5. 750GX Microprocessor Instruction Summary—Control MMUs (Page 1 of 2)

Instruction Description

mtsr SR,rS

Move-to Segment Register

SR[SR#]

← rS

mtsrin rS,rB

Move-to Segment Register Indirect

SR[rB[0–3]]

←rS

mfsr rD,SR

Move-from Segment Register

rD

←SR[SR#]

mfsrin rD,rB

Move-from Segment Register Indirect

rD

←SR[rB[0–3]]

Table 5-4. Other MMU Exception Conditions for the 750GX Processor (Page 2 of 2)

Condition Description Exception