User’s Manual

IBM PowerPC 750GX and GL RISC Microprocessor

Exceptions

Page 152 of 377

gx_04.fm.(1.2)

March 27, 2006

Note: The PowerPC Architecture documentation refers to exceptions as interrupts. In this book, the term

“interrupt” is reserved to refer to asynchronous exceptions and sometimes to the event that causes the

exception. The PowerPC Architecture also uses the word “exception” to refer to IEEE-defined floating-point

exception conditions that can cause a program exception to be taken (see Section 4.5.7, Program Exception

(0x00700), on page 170). The occurrence of these IEEE exceptions might not cause an exception to be

taken. IEEE-defined exceptions are referred to as IEEE floating-point exceptions or floating-point exceptions.

4.1 PowerPC 750GX Microprocessor Exceptions

As specified by the PowerPC Architecture, exceptions can be either precise or imprecise and either synchro-

nous or asynchronous. Asynchronous exceptions are caused by events external to the processor’s execu-

tion; synchronous exceptions are caused by instructions. The types of exceptions are shown in Table 4-1.

Note: All exceptions except for the system management interrupt, thermal management, and performance-

monitor exception are defined, at least to some extent, by the PowerPC Architecture.

These classifications are discussed in greater detail in Section 4.2, Exception Recognition and Priorities, on

page 153. For a better understanding of how the 750GX implements precise exceptions, see Chapter 6,

“Exceptions” of the PowerPC Microprocessor Family: The Programming Environments Manual. Exceptions

implemented in 750GX, and conditions that cause them, are listed in Table 4-2.

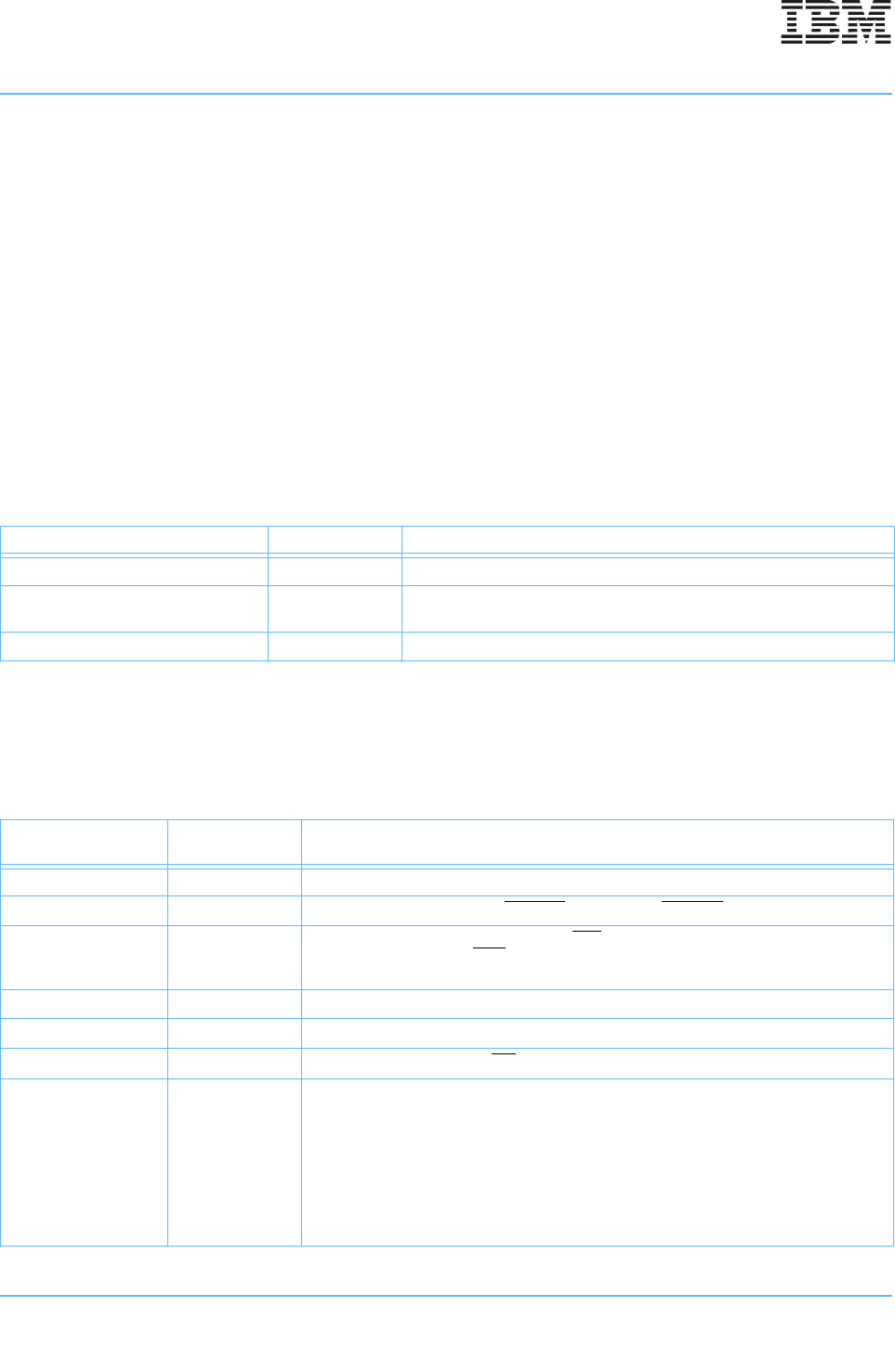

Table 4-1. PowerPC 750GX Microprocessor Exception Classifications

Synchronous/Asynchronous Precise/Imprecise Exception Types

Asynchronous, nonmaskable Imprecise Machine check, system reset

Asynchronous, maskable Precise

External interrupt, decrementer, system management interrupt,

performance-monitor interrupt, thermal-management interrupt

Synchronous Precise Instruction-caused exceptions

Table 4-2. Exceptions and Conditions (Page 1 of 2)

Exception Type

Vector Offset

(hex)

Causing Conditions

Reserved 00000 —

System reset 00100 Assertion of either hard reset (HRESET

) or soft reset (SRESET) at power-on reset.

Machine check 00200

Assertion of transfer error acknowledge (TEA

) during a data-bus transaction; assertion of

machine-check interrupt (MCP

); an address, data or L2 double-bit error. MSR[ME] must

be set.

DSI 00300 As specified in the PowerPC Architecture, if a page fault occurs.

ISI 00400 As defined by the PowerPC Architecture, if a page fault occurs.

External interrupt 00500 MSR[EE] = 1, and interrupt (INT

) is asserted.

Alignment 00600

• A floating-point load/store, Store Multiple Word (stmw), Store Word Conditional

Indexed (stwcx.

), Load Multiple Word (lmw), Load String Word Indexed (lwarx),

External Control In Word Indexed (eciwx), or External Control Out Word Indexed

(ecowx

) instruction operand is not word-aligned.

• A multiple/string load/store operation is attempted in little-endian mode.

• An operand of a Data Cache Block Set to Zero (dcbz) instruction is on a page that is

write-through or cache-inhibited for a virtual mode access.

• An attempt to execute a dcbz instruction occurs when the cache is disabled.