User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Performance Monitor and System Related Features

Page 350 of 377

gx_11.fm.(1.2)

March 27, 2006

As a result of a performance-monitor exception being taken, the action taken depends on the programmable

events. To help track which part of the code was being executed when an exception was signaled, the

address of the last completed instruction during that cycle is saved in the Sampled Instruction Address (SIA)

register. The SIA is not updated if no instruction completed the cycle in which the exception was taken.

Exception handling for the Performance-Monitor Interrupt Exception is described in Section 4.5.13, Perfor-

mance-Monitor Interrupt (0x00F00), on page 172.

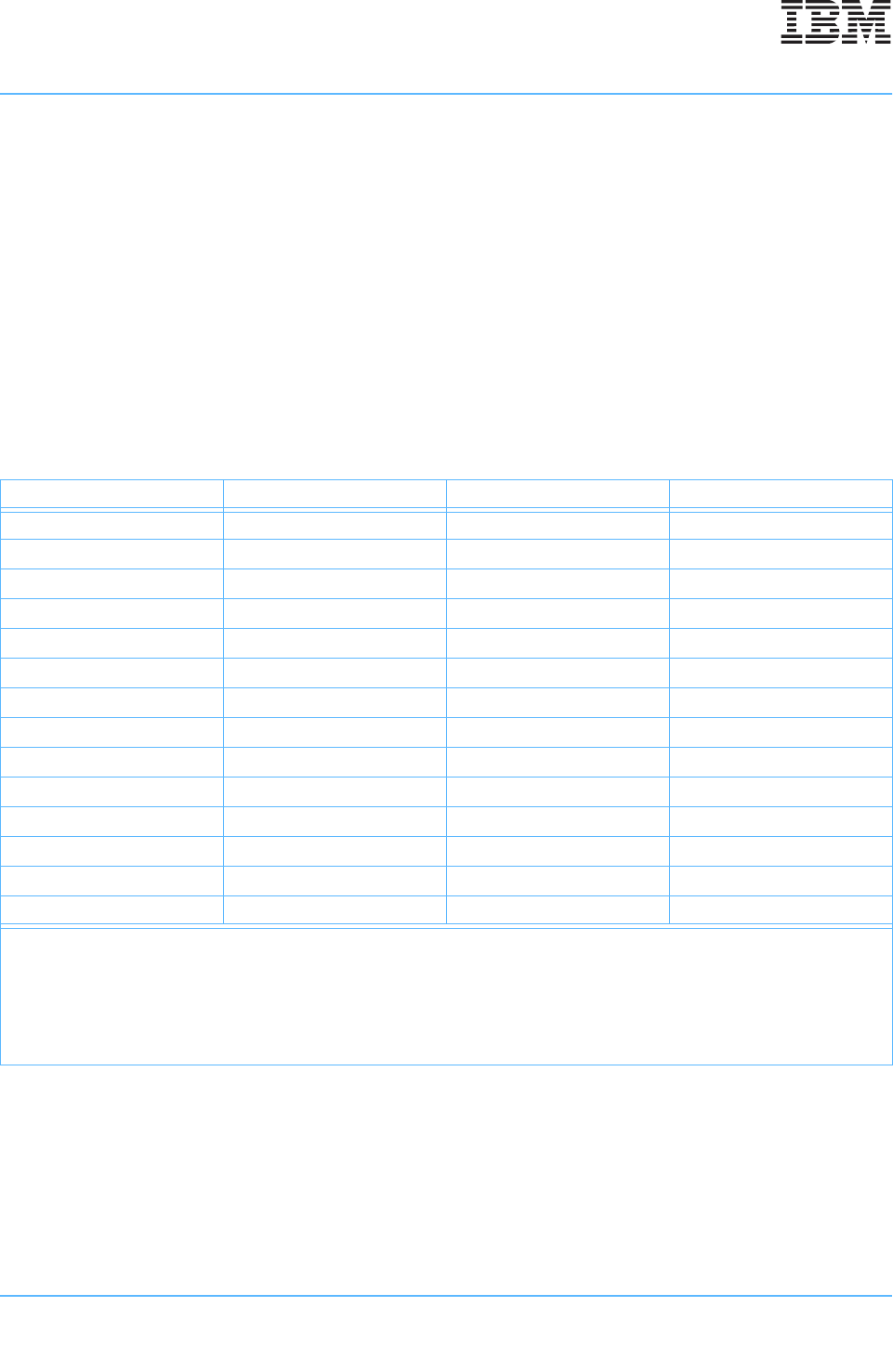

11.2 Special-Purpose Registers Used by Performance Monitor

The performance monitor incorporates the SPRs listed in Table 11-1. All of these supervisor-level registers

are accessed through Move-to Special Purpose Register (mtspr) and Move-from Special Purpose Register

(mfspr) instructions.

Table 11-1. Performance Monitor SPRs

SPR Number SPR[5-9] || SPR[0-4] Register Name Access Level

952 11101 11000 MMCR0 Supervisor

953 11101 11001 PMC1 Supervisor

954 11101 11010 PMC2 Supervisor

955 11101 11011 SIA Supervisor

956 11101 11100 MMCR1 Supervisor

957 11101 11101 PMC3 Supervisor

958 11101 11110 PMC4 Supervisor

936 11101 01000 UMMCR0 User (read only)

937 11101 01001 UPMC1 User (read only)

938 11101 01010 UPMC2 User (read only)

939 11101 01011 USIA User (read only)

940 11101 01100 UMMCR1 User (read only)

941 11101 01101 UPMC3 User (read only)

942 11101 01110 UPMC4 User (read only)

Notes:

• The user registers (UMMCR0, UMMCR1, UPMC1, and so on) contain the same values as the nonuser registers but provide read-

only access to the Performance-Monitor Registers while in user mode. An attempt to write to a user register in either supervisor or

user mode results in a program interrupt.

• Reading and writing these registers does not synchronize the machine. An explicit synchronization instruction should be placed

before and after a Move-from Special Purpose Register (mfspr) or Move-to Special Purpose Register (mtspr) instruction to one of

these registers to ensure an accurate count.