User’s Manual

IBM PowerPC 750GX and 750GL RISC Microprocessor

Instruction Timing

Page 214 of 377

gx_06.fm.(1.2)

March 27, 2006

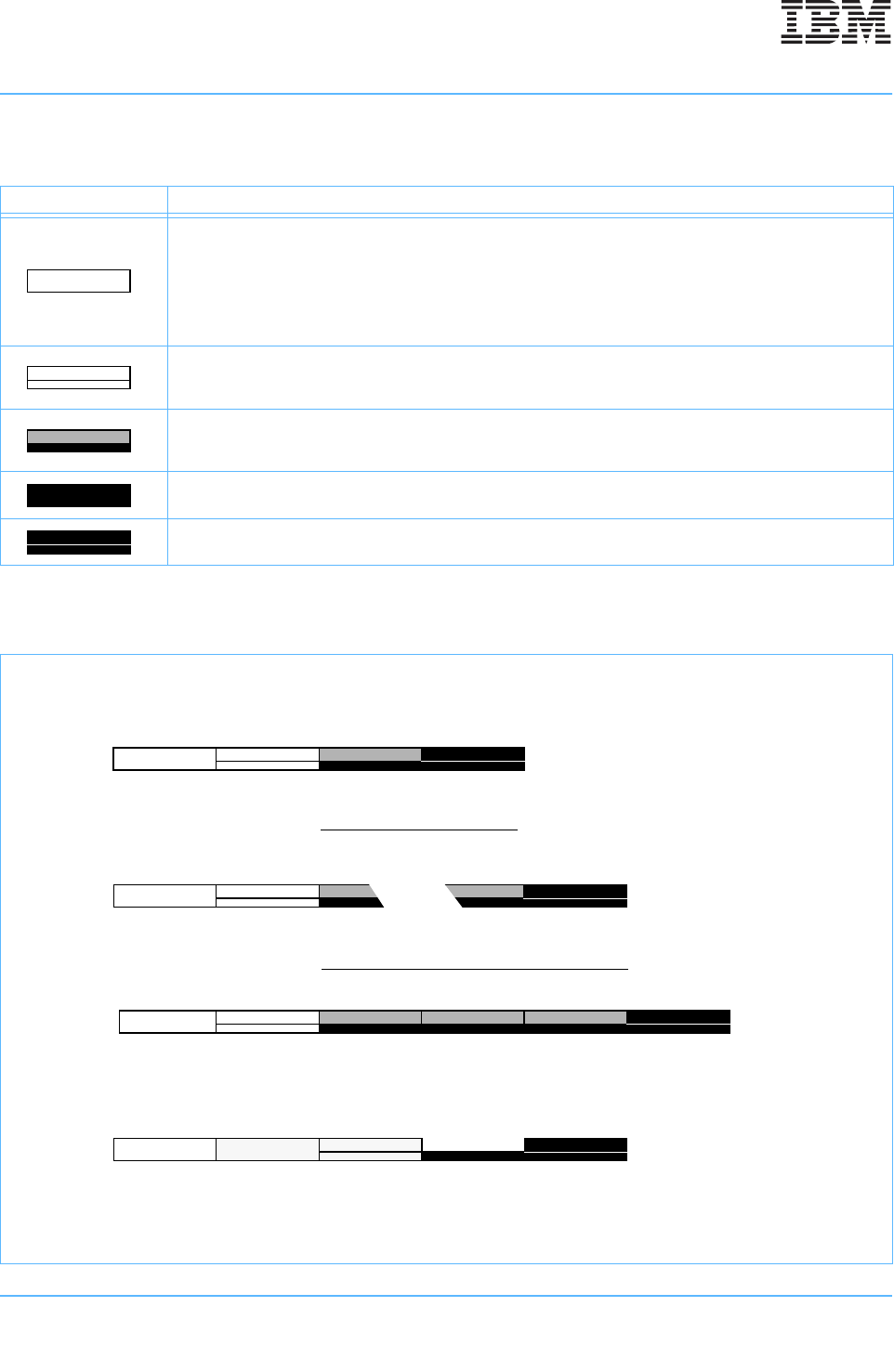

The notation conventions used in the instruction timing examples are as follows:

Figure 6-3 shows the stages of the 750GX’s execution units.

Table 6-1. Notation Conventions for Instruction Timing

Symbol Description

Fetch. The fetch stage includes the time between when an instruction is requested and when it is brought into

the instruction queue. This latency can vary, depending upon whether the instruction is in the branch target

instruction cache (BTIC), the L1 instruction cache, the L2 cache, or system memory (in which case latency

can be affected by bus speed and traffic on the system bus, and address-translation issues). Therefore, in the

examples in this chapter, the fetch stage is usually idealized. That is, an instruction is usually shown to be in

the fetch stage when it is a valid instruction in the instruction queue. The instruction queue has six entries,

IQ0–IQ5.

In dispatch entry (IQ0/IQ1). Instructions can be dispatched from IQ0 and IQ1. Because dispatch is instanta-

neous, it is perhaps more useful to describe it as an event that marks the point in time between the last cycle

in the fetch stage and the first cycle in the execute stage.

Execute. The operations specified by an instruction are being performed by the appropriate execution unit.

The black stripe is a reminder that the instruction occupies an entry in the completion queue, described in

Figure 6-3.

Complete. The instruction is in the completion queue. In the final stage, the results of the executed instruction

are written back, and the instruction is retired. The completion queue has six entries, CQ0–CQ5.

In retirement entry. Completed instructions can be retired from CQ0 and CQ1. Like dispatch, retirement is an

event that, in this case, occurs at the end of the final cycle of the complete stage.

Figure 6-3. PowerPC 750GX Microprocessor Pipeline Stages

Fetch In Dispatch Execute1 Complete/Retire

Fetch In Dispatch Complete/RetireEA

Fetch In Dispatch Complete/Retire

IU1/IU2/SRU Instructions

LSU Instructions

FPU Instructions

Normalize

Multiply Add Round/

1. Several integer instructions, such as multiply and divide instructions, require multiple cycles in the execute stage.

Execute

Execute

Calculation

Cache Align

Entry

Entry

Entry

BPU Instructions

Fetch Fetch

Predict

Complete/Retire2In Dispatch

Entry

In Completion

Queue2

2. Only those branch instructions that update the LR or CTR take an entry in the completion queue.