Rev.1.10 Jul 01, 2005 page 137 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

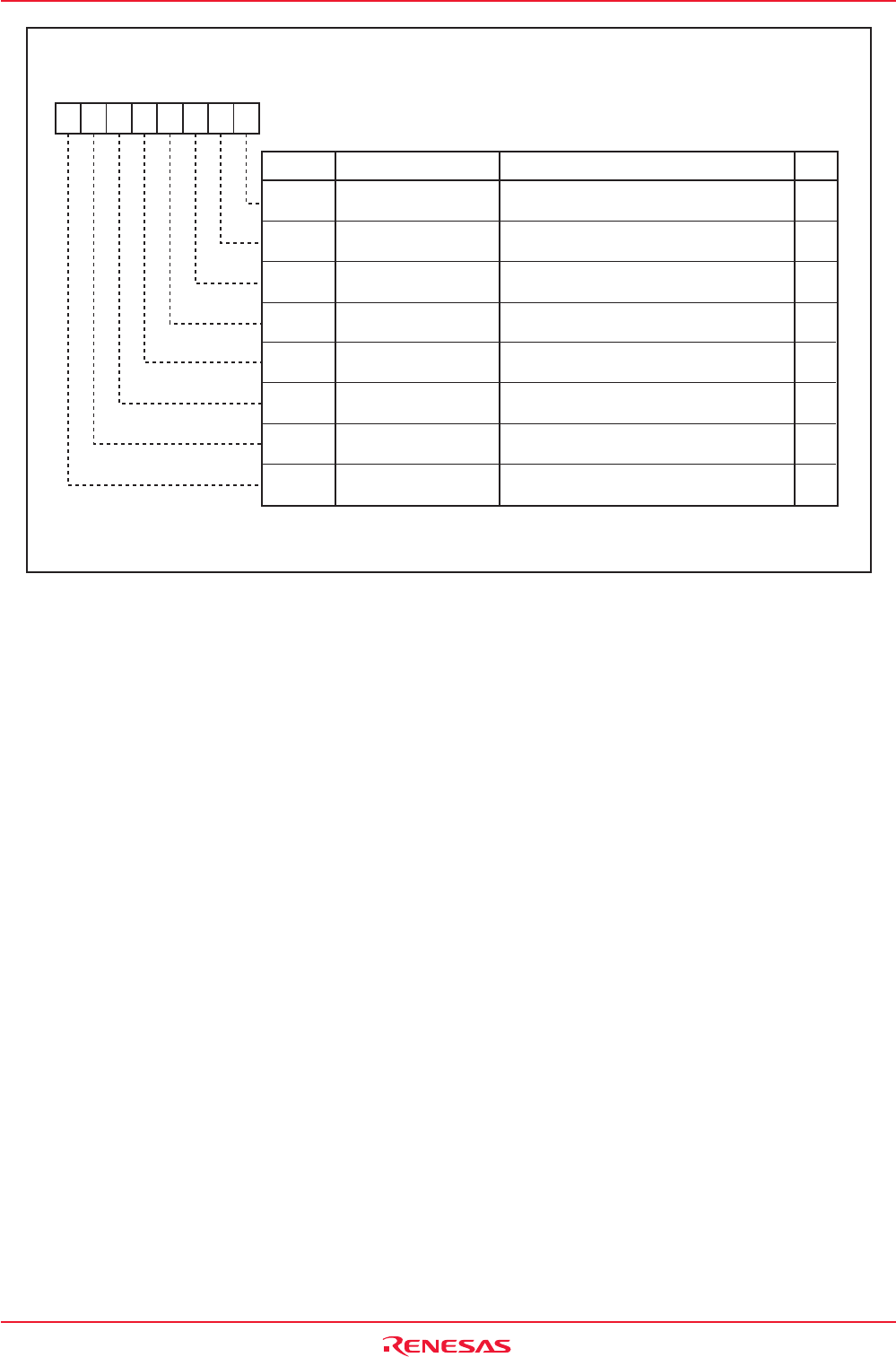

Figure 14.10 U0SMR4 to U2SMR4 Registers

b7 b6 b5 b4 b3 b2 b1 b0

Function

UARTi Special Mode Register 4 (i = 0 to 2)

Bit Name

Bit

Symbol

Symbol Address After Reset

U0SMR4 to U2SMR4 01ECh, 01F0h, 01F4h 00h

RW

STAREQ

RSTAREQ

STPREQ

Restart Condition

Generate Bit

(1)

Stop Condition

Generate Bit

(1)

Start Condition

Generate Bit

(1)

STSPSEL

SCL,SDA Output

Select Bit

0 : Clear

1 : Start

0 : Clear

1 : Start

0 : Clear

1 : Start

0 : Start and stop conditions not output

1 : Start and stop conditions output

RW

RW

RW

RW

SCL Wait Bit 3SWC9

0 : SCL "L" hold disabled

1 : SCL "L" hold enabled

RW

SCL Output Stop

Enable Bit

SCLHI

0 : Disabled

1 : Enabled

RW

ACK Data Output

Enable Bit

ACKC

0 : Serial I/O data output

1 : ACK data output

RW

ACK Data BitACKD

0 : ACK

1 : NACK

RW

NOTE:

1. Set to "0" when each condition is generated.