Rev.1.10 Jul 01, 2005 page 223 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 18. CAN Module

Under development

This document is under development and its contents are subject to change.

18.15.1 Reception

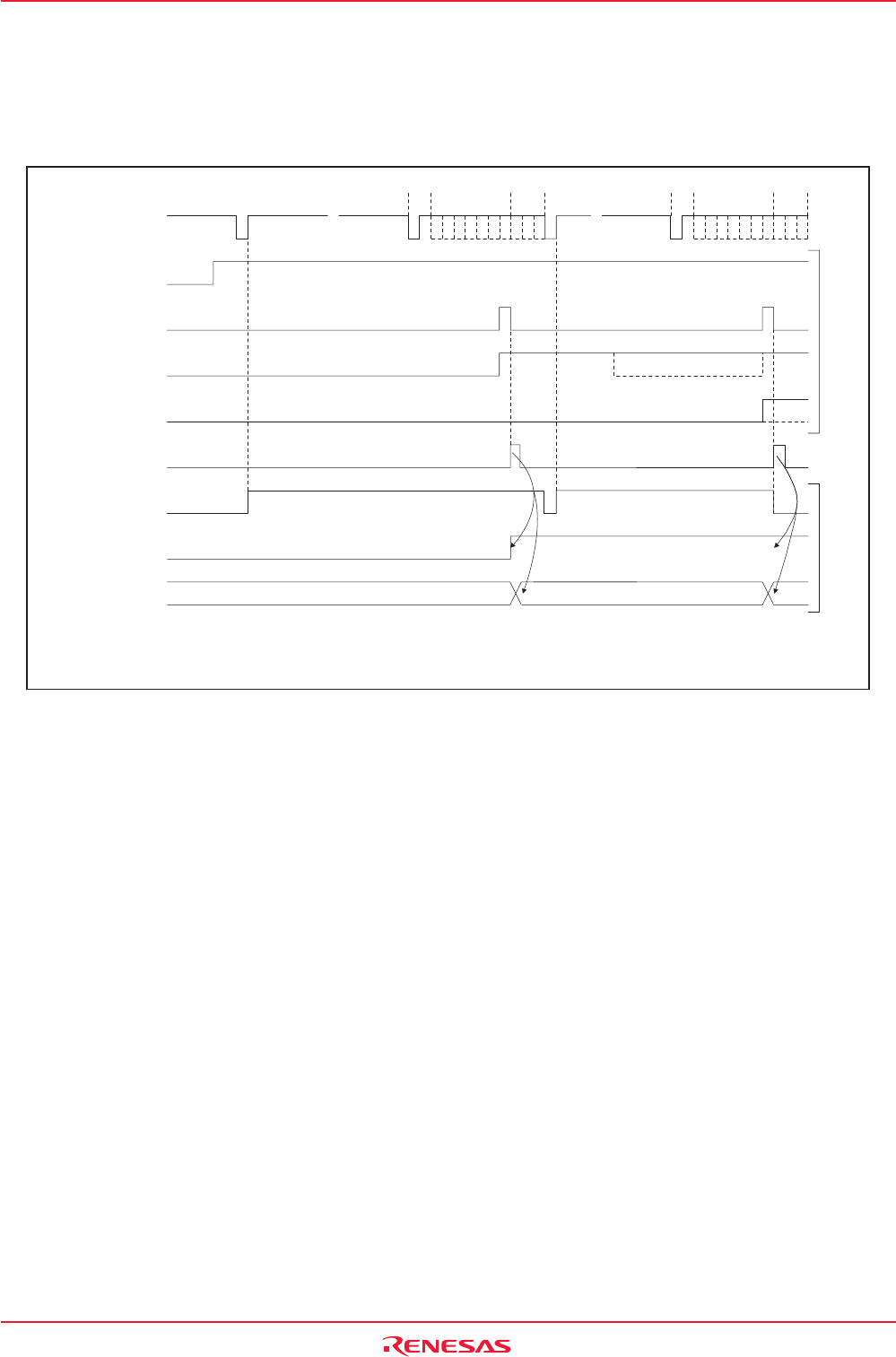

Figure 18.20 shows the behavior of the module when receiving two consecutive CAN messages, that fit

into the slot of the shown CiMCTLj register (i = 0, 1, j = 0 to 15) and leads to losing/overwriting of the first

message.

CANbus

RecReq bit

InvalData bit

CANi Successful

Reception Interrupt

RecState bit

RecSucc bit

MBOX bit

NewData bit

SOF ACK EOF EOFIFS

IFS

SOF

Receive slot No.

MsgLost bit

CiMCTLj register

CiSTR register

(1)

(2)

(2)

(3)

(4)

(5)

(5)

(5)

i = 0, 1

j = 0 to 15

ACK

Figure 18.20 Timing of Receive Data Frame Sequence

(1) On monitoring a SOF on the CAN bus the RecState bit in the CiSTR register becomes “1” (CAN

module is receiver) immediately, given the module has no transmission pending.

(2) After successful reception of the message, the NewData bit in the CiMCTLj register of the receiving

slot becomes “1” (stored new data in slot). The InvalData bit in the CiMCTLj register becomes “1”

(message is being updated) at the same time and the InvalData bit becomes “0” (message is valid)

again after the complete message was transferred to the slot.

(3) When the interrupt enable bit in the CiICR register of the receiving slot = 1 (interrupt enabled), the

CANi successful reception interrupt request is generated and the MBOX bit in the CiSTR register is

changed. It shows the slot number where the message was stored and the RecSucc bit in the CiSTR

register is active.

(4) Read the message out of the slot after setting the New Data bit to “0” (the content of the slot is read or

still under processing by the CPU) by a program.

(5) If the NewData bit is set to “0” by a program or the next CAN message is received successfully before

the receive request for the slot is canceled, the MsgLost bit in the CiMCTLj register is set to “1”

(message has been overwritten). The new received message is transferred to the slot. Generating of

an interrupt request and change of the CiSTR register are same as in 3).