Rev.1.10 Jul 01, 2005 page 6 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 1. Overview

Under development

This document is under development and its contents are subject to change.

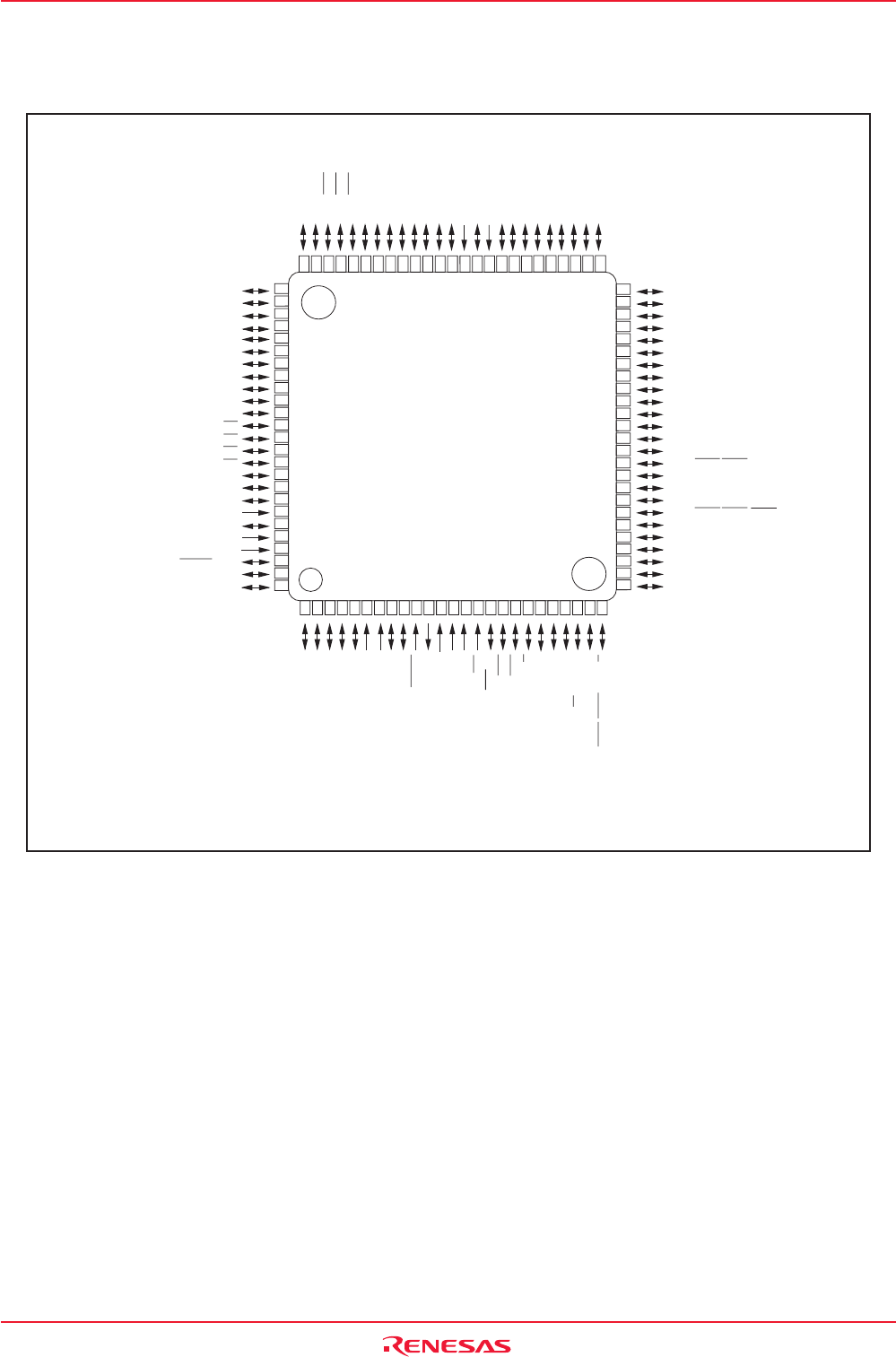

PIN CONFIGURATION (top view)

Figure 1.3 Pin Configuration (Top View) (1)

1.5 Pin Configuration

Figures 1.3 and 1.4 show the pin configuration (top view).

1 2 3 4 5 6 7 8 910111213141516171819202122232425

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

515253545556

57585960616263646566676869707172737475

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

P0_0/AN0_0

P0_1/AN0_1

P0_2/AN0_2

P0_3/AN0_3

P0_4/AN0_4

P0_5/AN0_5

P0_6/AN0_6

P0_7/AN0_7

P1_0

P1_1

P1_2

P1_3

P1_4

VREF

AVSS

VCC1

XIN

XOUT

VSS

RESET

CNVSS

P8_7/XCIN

P8_6/XCOUT

BYTE

P2_0/AN2_0

P2_1/AN2_1

P2_2/AN2_2

P2_3/AN2_3

P2_4/AN2_4

P2_5/AN2_5

P2_6/AN2_6

P2_7/AN2_7

P3_0

P3_1

P3_2

P3_3

P3_4

P3_5

P3_6

P3_7

P4_0

P4_1

P4_2

P4_3

P7_4/TA2OUT/W/(CLK4)

P7_6/TA3OUT/CTX1

P5_6

P7_7/TA3IN/CRX1

P5_5

P5_4

P5_3

P5_2

VCC2

VSS

P5_7/CLKOUT

P4_5

P4_6

P4_7

AVCC

P6_3/TXD0/SDA0

P6_5/CLK1

P6_6/RXD1/SCL1

P6_7/TXD1/SDA1

P6_1/CLK0

P6_2/RXD0/SCL0

P10_0/AN0

P10_1/AN1

P10_2/AN2

P10_3/AN3

P9_3/DA0/TB3IN

P9_4/DA1/TB4IN

P9_5/ANEX0/CRX0/CLK4

P9_6/ANEX1/CTX0/SOUT4

(1)

P9_1/TB1IN/SIN3

P9_2/TB2IN/SOUT3

P8_0/TA4OUT/U/(SIN4)

P6_0/CTS0/RTS0

P6_4/CTS1/RTS1/CTS0/CLKS1

P8_2/INT0

P8_3/INT1

P8_5/NMI

P9_7/ADTRG/SIN4

P4_4

P5_0

P5_1

P9_0/TB0IN/CLK3

P8_4/INT2/ZP

P7_2/CLK2/TA1OUT/V

P7_1/RXD2/SCL2/TA0IN/TB5IN

(1)

P7_0/TXD2/SDA2/TA0OUT

P7_5/TA2IN/W/(SOUT4)

P7_3/CTS2/RTS2/TA1IN/V

P1_5/INT3

P1_6/INT4

P1_7/INT5

P10_7/AN7/KI3

P10_6/AN6/KI2

P10_5/AN5/KI1

P10_4/AN4/KI0

P8_1/TA4IN/U

M16C/6N Group

(M16C/6NK)

Package: PLQP0100KB-A

NOTE:

1. P7_1 and P9_1 are N channel open-drain pins.