Rev.1.10 Jul 01, 2005 page 58 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 7. Clock Generating Circuit

Under development

This document is under development and its contents are subject to change.

7.5.3 How to Use Oscillation Stop and Re-oscillation Detection Function

• The oscillation stop, re-oscillation detection interrupt shares the vector with the watchdog timer interrupt.

If the oscillation stop, re-oscillation detection and watchdog timer interrupts both are used, read the

CM22 bit in an interrupt routine to determine which interrupt source is requesting the interrupt.

• Where the main clock re-oscillated after oscillation stop, the clock source for CPU clock and peripheral

function must be switched to the main clock in the program. Figure 7.14 shows the procedure to switch

the clock source from the on-chip oscillator to the main clock.

• Simultaneously with oscillation stop, re-oscillation detection interrupt request occurrence, the CM22 bit

becomes “1”. When the CM22 bit is set at “1”, oscillation stop, re-oscillation detection interrupt are

disabled. By setting the CM22 bit to “0” in the program, oscillation stop, re-oscillation detection interrupt

are enabled.

• If the main clock stops during low speed mode where the CM20 bit is “1”, an oscillation stop, re-oscillation

detection interrupt request is generated. At the same time, the on-chip oscillator starts oscillating. In this

case, although the CPU clock is derived from the sub clock as it was before the interrupt occurred, the

peripheral function clocks now are derived from the on-chip oscillator clock.

• To enter wait mode while using the oscillation stop and re-oscillation detection function, set the CM02

bit to “0” (peripheral function clocks not turned off during wait mode).

• Since the oscillation stop and re-oscillation detection function is provided in preparation for main clock

stop due to external factors, set the CM20 bit to “0” (oscillation stop, re-oscillation detection function

disabled) where the main clock is stopped or oscillated in the program, that is where the stop mode is

selected or the CM05 bit is altered.

• This function cannot be used if the main clock frequency is 2 MHz or less. In that case, set the CM20 bit to “0”.

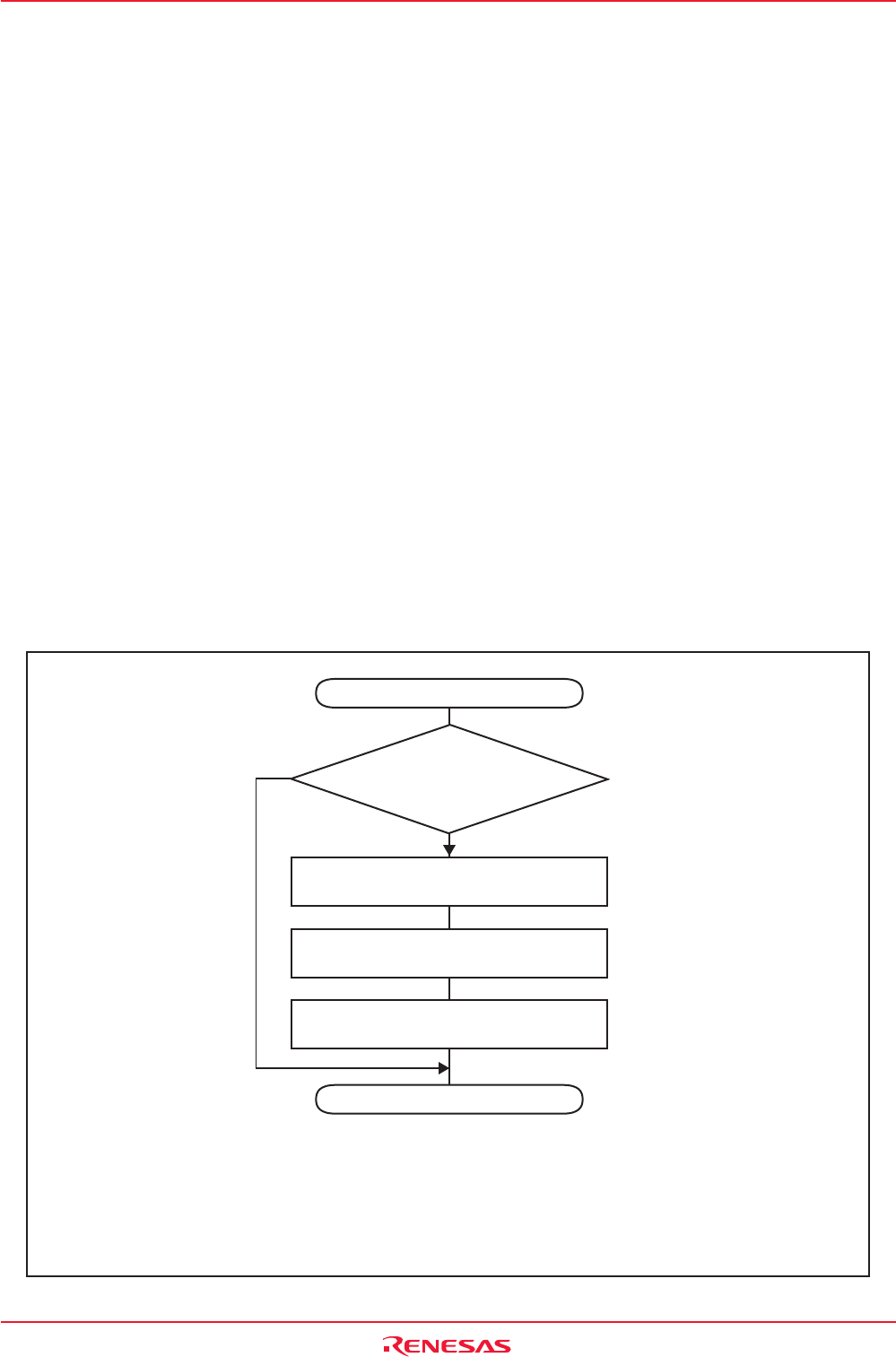

Figure 7.14 Procedure to Switch Clock Source from On-chip Oscillator to Main Clock

Switch the main clock

NO

YES

Determine several times

whether the CM23 bit is set to "0"

(main clock oscillates)

Set the CM22 bit to "0" (main clock stop,

re-oscillation not detected)

Set the CM06 bit to "1" (divide-by-8)

Set the CM21 bit to "0"

(main clock for the CPU clock source)

(1)

End

CM06 bit : Bit in CM0 register

CM21, CM22, CM 23 bits: Bits in CM2 register

NOTE:

1. If the clock source for CPU clock is to be changed to PLL clock,

set to PLL operation mode after set to high-speed mode.