Rev.1.10 Jul 01, 2005 page 179 of 318

REJ09B0124-0110

M16C/6N Group (M16C/6NK, M16C/6NM) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

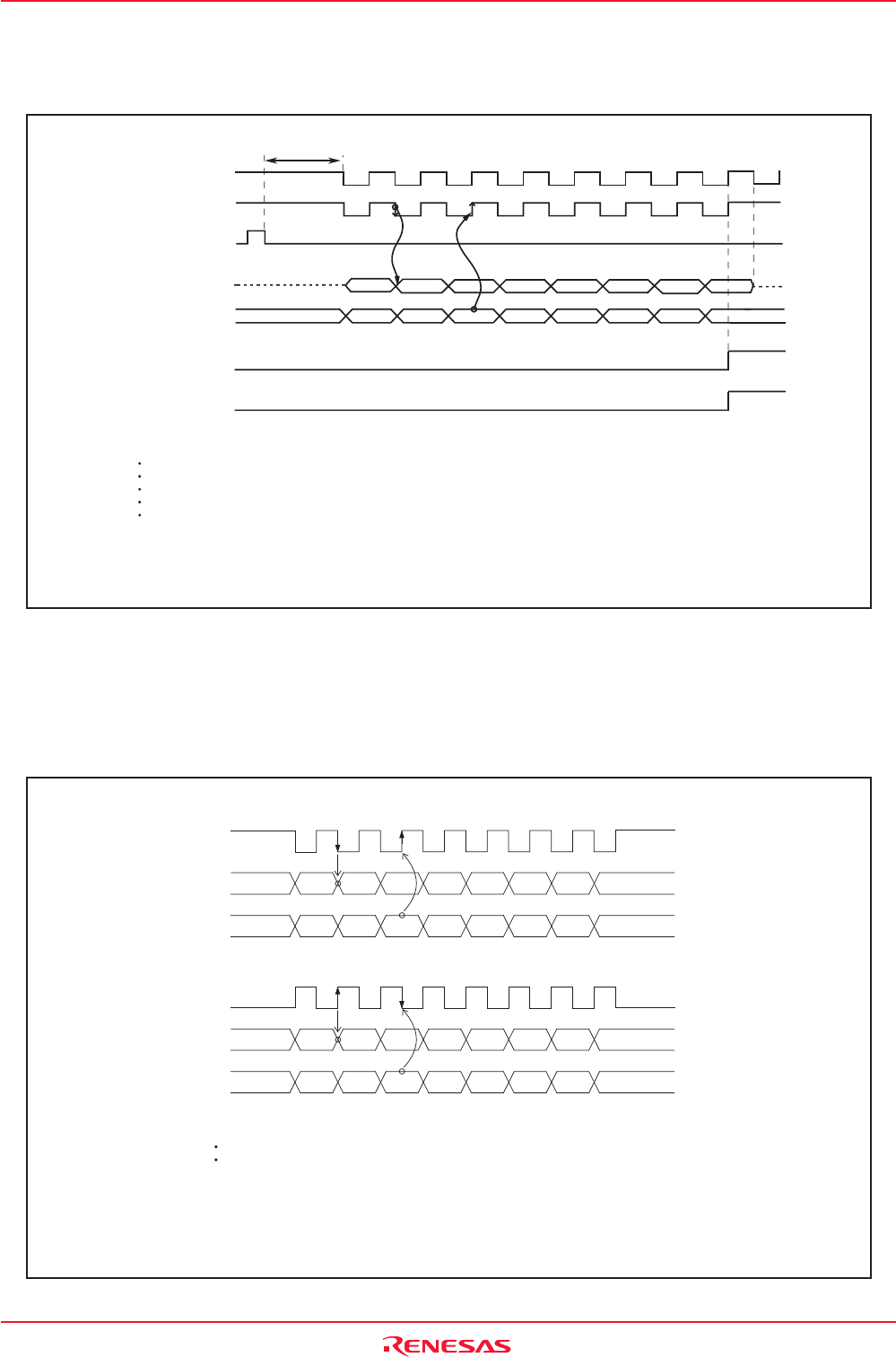

14.2.1 SI/Oi Operation Timing

Figure 14.39 shows the SI/Oi operation timing.

Figure 14.39 SI/Oi Operation Timing

14.2.2 CLK Polarity Selection

The SMi4 bit in the SiC register allows selection of the polarity of the transfer clock.

Figure 14.40 shows the polarity of the transfer clock.

Figure 14.40 Polarity of Transfer Clock

D7D0 D1 D2 D3 D4 D5 D6

1.5 cycle (max.)

(NOTE 2)

(1)

SI/Oi internal clock

CLKi output

Signal written to the

SiTRR register

SOUTi output

SINi input

IR bit in SiIC register

"H"

"L"

"H"

"L"

"H"

"L"

"H"

"L"

"H"

"L"

"1"

"0"

SiTRF bit in

S3456TRR register

"1"

"0"

i = 3 to 6 (5 and 6 are only in the 128-pin version.)

* This diagram applies to the case where the bits in the SiC register are set as follows:

SMi2 = 0 (SOUTi output)

SMi3 = 1 (SOUTi output, CLKi function)

SMi4 = 0 (transmit data output at the falling edge and receive data input at the rising edge of the transfer clock)

SMi5 = 0 (LSB first)

SMi6 = 1 (internal clock)

NOTES:

1.If the SMi6 bit = 1 (internal clock), the serial I/O starts sending or receiving data a maximum of 1.5 transfer clock cycles after writing to the

SiTRR register.

2.When the SMi6 bit = 1 (internal clock), the SOUTi pin is placed in the high-impedance state after the transfer finishes.

D1 D2 D3 D4 D5 D6 D7

D1 D2 D3 D4 D5 D6 D7

D0

D0

SOUTi

SINi

CLKi

D1 D2 D3 D4 D5 D6 D7D0

D1 D2 D3 D4 D5 D6 D7D0

SOUTi

SINi

CLKi

(2) When SMi4 bit in SiC register = 1

(1) When SMi4 bit in SiC register = 0

i = 3 to 6 (5 and 6 are only in the 128-pin version.)

*This diagram applies to the case where the bits in the SiC register are set as follows:

SMi5 = 0 (LSB first)

SMi6 = 1 (internal clock)

NOTES:

1.When the SMi6 bit = 1 (internal clock), a high level is output from the CLKi pin if not

transferring data.

2.When the SMi6 bit = 1 (internal clock), a low level is output from the CLKi pin if not

transferring data.

(NOTE 2)

(NOTE 1)