System Clocking Configuration window 79

Models 2616RC, 3096RC & 3196RC Admin Reference Guide 6 • System Clocking

Main Reference (sysgshDSLClockMainRef) and Fallback Reference (sysgshDSLClockFallbackRef)

When a T-DAC’s clocking mode is defined to be Master or Secondary, the T-DAC System Clocking Configura-

tion window displays the Main Reference and Fallback Reference parameters. When a T-DACS clocking mode is

defined to be Slave, the Main Reference and Fallback Reference parameters do not apply. In slave mode, the T-

DAC hides the Main Reference and Fallback Reference parameters to make them inaccessible (See figure 27).

The T-DAC will use the fallback reference if and only if the primary reference becomes unavailable. By default,

the clocking Fallback System is factory-disabled. To activate the T-DAC’s fallback system you must enable it

(see section“Enable/Disable Fallback System” on page 82).

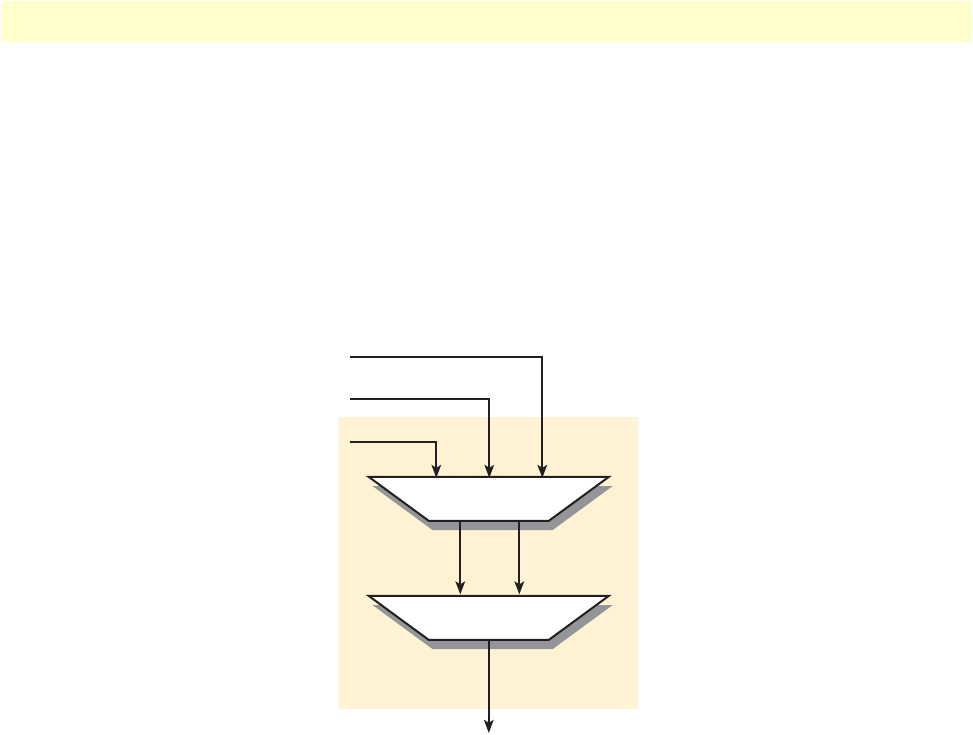

Figure 27. Clocking scheme for Master and Secondary Cards

When defining the primary and secondary clocking sources, you can select any one of the T-DAC’s WAN

ports, the T-DAC internal clock pulse oscillator, or building integrated system timing (BITS). Both parameters

will be defined from the same set of possible values. For the fallback reference to serve its purpose, however,

you must define it by selecting a value different from the main reference.

The T-DAC will use the main reference as its system clocking source unless the main reference fails or becomes

disconnected. When the primary reference becomes unavailable 3096RC will switch to the fallback reference as

its system clocking source.

You must also enable the T-DAC’s fallback mechanism (see section“Enable/Disable Fallback System” on

page 82). For the T-DAC’s main and fallback clocking references, you can choose:

• One of the T-DAC 4, 8, 12, or 16 WAN ports

• An internal oscillator residing within the T-DAC

• External—BITS clock (building integrated timing system)

Note

For the external BITS clock setting to operate, you must connect the

BITS clock system at the installation site to the EXT CLOCK con-

nector on one of the WAN Access Modules installed in the rear of the

ForeFront chassis.

Main Reference

BITS

Internal

T1/E1 (1:16)

Fallback Reference

Master or Secondary

clock to backplane