S3C2440A RISC MICROPROCESSOR ARM INSTRUCTION SET

3-43

Rn

1

R1

R1

2

R5

3

R1

R5

4

R7

Rn

0x100C

0x1000

0x0FF4

0x100C

0x1000

0x0FF4

0x100C

0x1000

0x0FF4

0x100C

0x1000

0x0FF4

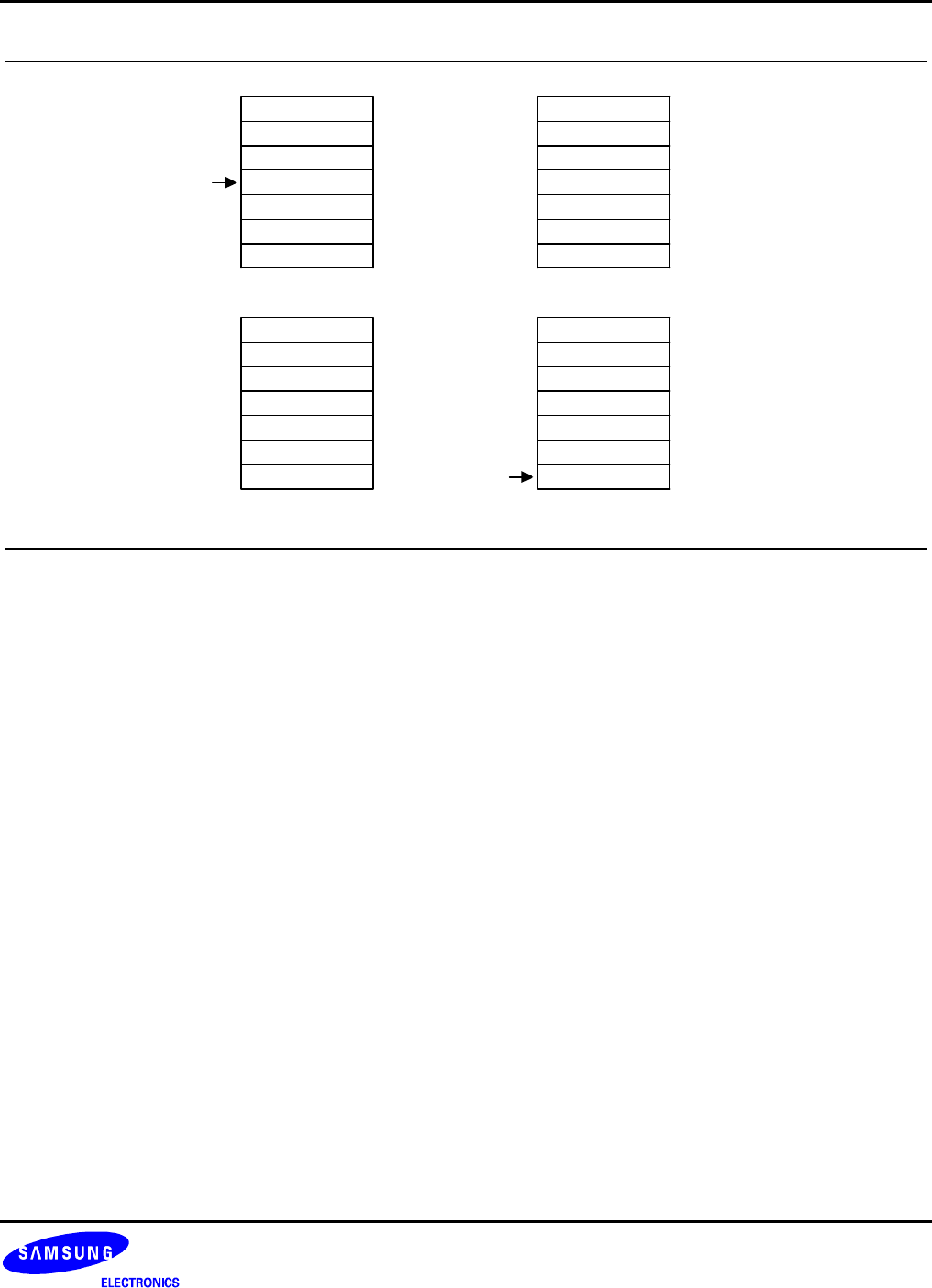

Figure 3-22. Pre-Decrement Addressing

USE OF THE S BIT

When the S bit is set in a LDM/STM instruction it depends on R15 is available in the transfer list and on the type of

instruction. The S bit should only be set if the instruction is to execute in a privileged mode.

LDM with R15 in Transfer List and S Bit Set (Mode Changes)

If the instruction is a LDM then SPSR_<mode> is transferred to CPSR at the same time as R15 is loaded.

STM with R15 in Transfer List and S Bit Set (User Bank Transfer)

The registers transferred are taken from the User bank rather than the bank corresponding to the current mode.

This is useful for saving the user state on process switches. Base write-back should not be used when this

mechanism is employed.

R15 not in List and S Bit Set (User Bank Transfer)

For both LDM and STM instructions, the User bank registers are transferred rather than the register bank

corresponding to the current mode. This is useful for saving the user state on process switches. Base write-back

should not be used when this mechanism is employed.

When the instruction is LDM, care must be taken not to read from a banked register during the following cycle

(inserting a dummy instruction such as MOV R0, R0 after the LDM will ensure safety).

USE OF R15 AS THE BASE

R15 should not be used as the base register in any LDM or STM instruction.