S3C2440A RISC MICROPROCESSOR SPI

22-7

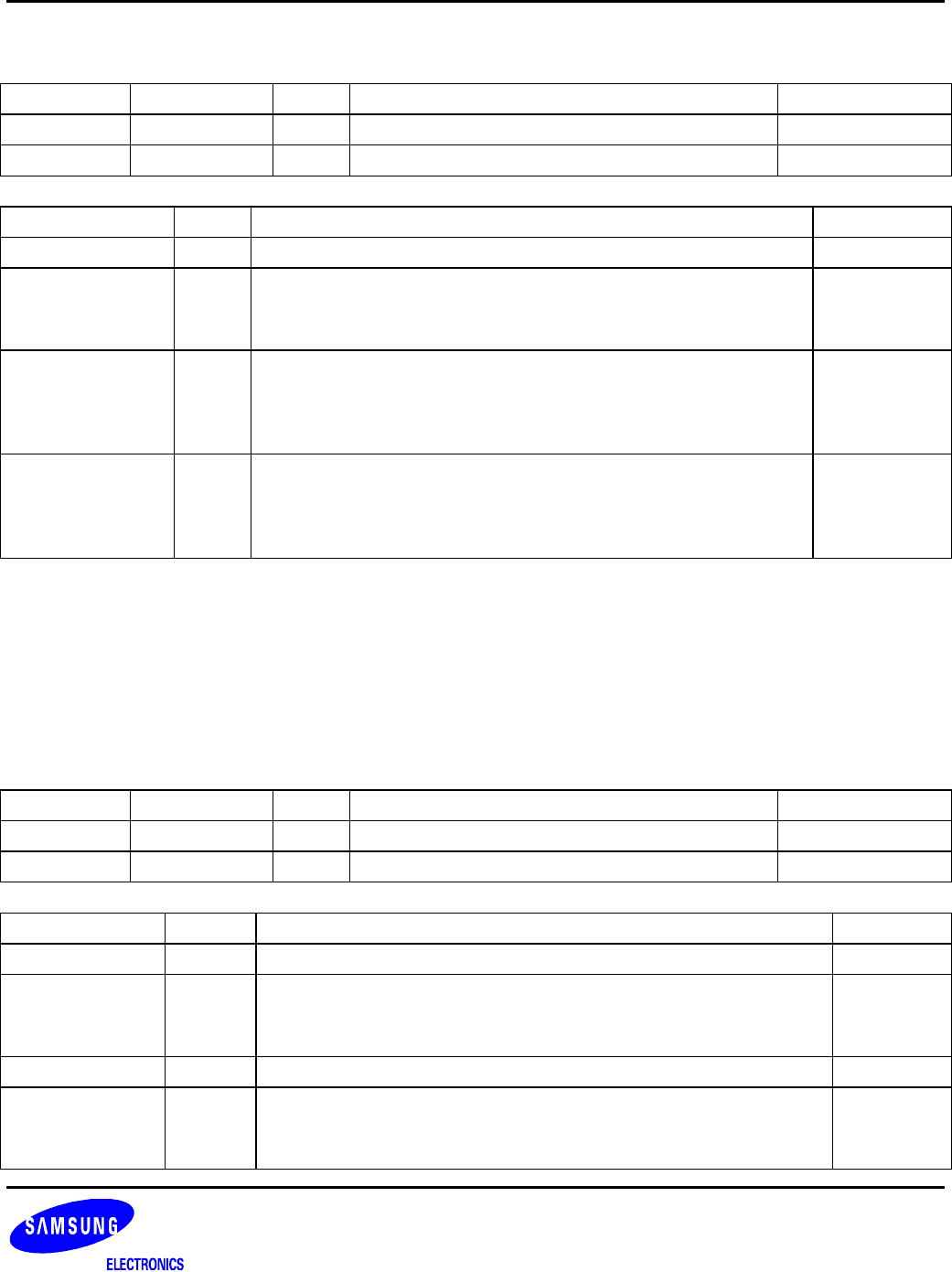

SPI STATUS REGISTER

Register Address R/W Description Reset Value

SPSTA0 0x59000004 R SPI channel 0 status register 0x01

SPSTA1 0x59000024 R SPI channel 1 status register 0x01

SPSTAn Bit Description Initial State

Reserved [7:3]

Data Collision

Error Flag (DCOL)

[2] This flag is set if the SPTDATn is written or SPRDATn is read while

a transfer is in progress and cleared by reading the SPSTAn.

0 = not detect 1 = collision error detect

0

Multi Master Error

Flag (MULF)

[1] This flag is set if the nSS signal goes to active low while the SPI is

configured as a master, and SPPINn's ENMUL bit is multi master

error detect mode. MULF is cleared by reading SPSTAn.

0 = not detect 1 = multi master error detect

0

Transfer Ready

Flag (REDY)

[0] This bit indicates that SPTDATn or SPRDATn is ready to transmit

or receive. This flag is automatically cleared by writing data to

SPTDATn.

0 = not ready 1 = data Tx/Rx ready

1

SPI PIN CONTROL REGISTER

When the SPI system is enabled, the direction of pins except nSS pin is controlled by MSTR bit of SPCONn

register. The direction of nSS pin is always input.

When the SPI is a master, nSS pin is used to check multi-master error, provided that the SPPIN's ENMUL bit is

active, and another GPIO should be used to select a slave.

If the SPI is configured as a slave, the nSS pin is used to select SPI as a slave by one master.

Register Address R/W Description Reset Value

SPPIN0 0x59000008 R/W SPI channel 0 pin control register 0x00

SPPIN1 0x59000028 R/W SPI channel 1 pin control register 0x00

SPPINn Bit Description Initial State

Reserved [7:3]

Multi Master error

detect Enable

(ENMUL)

[2] The nSS pin is used as an input to detect multi master error when

the SPI system is a master.

0 = disable (general purpose) 1 = multi master error detect enable

0

Reserved [1] Reserved 0

Master Out Keep

(KEEP)

[0] Determine MOSI drive or release when 1byte transmit is completed

(master only).

0 = release 1 = drive the previous level

0