DMA S3C2440A RISC MICROPROCESSOR

8-8

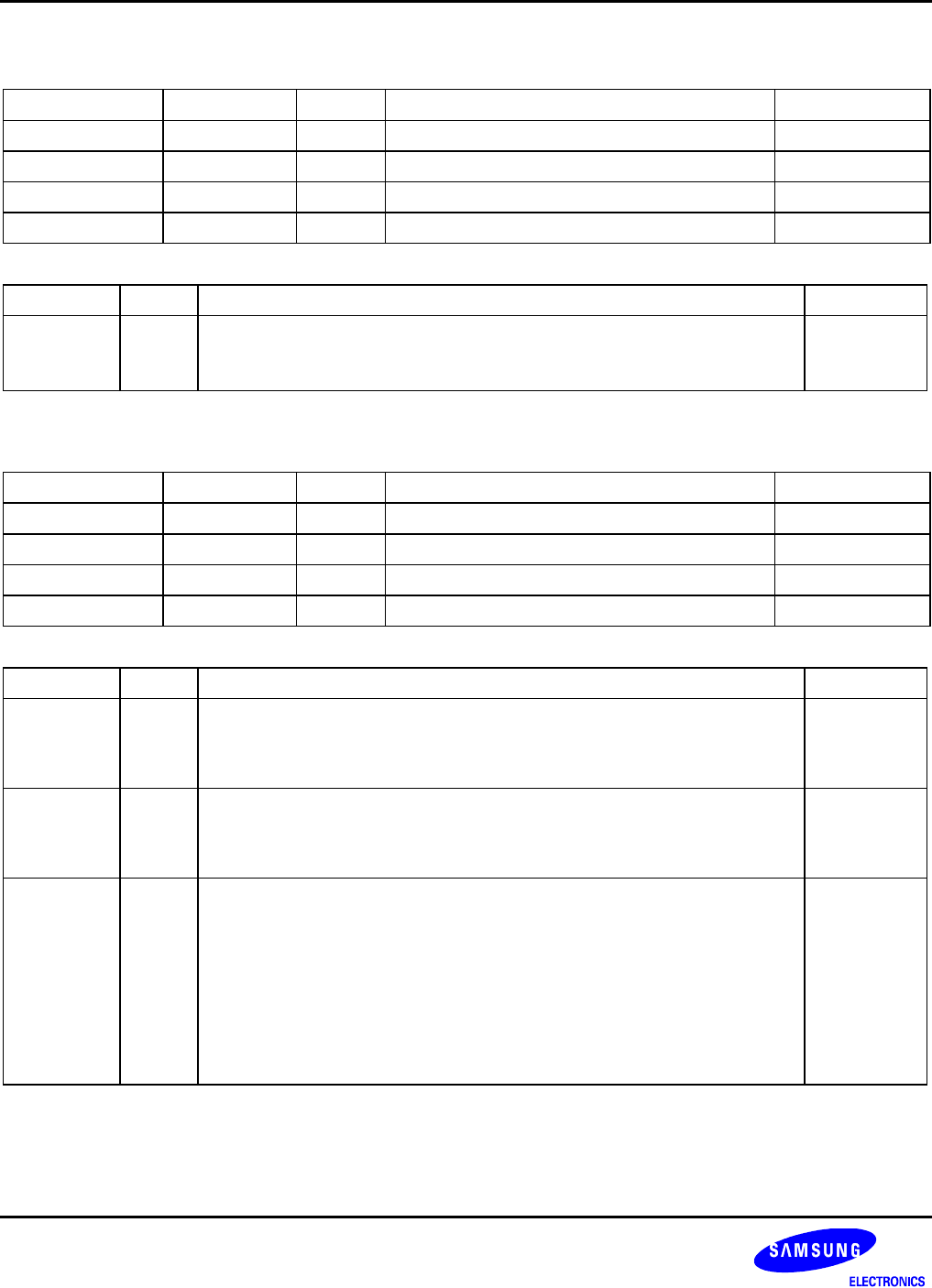

DMA INITIAL DESTINATION (DIDST) REGISTER

Register Address R/W Description Reset Value

DIDST0 0x4B000008 R/W DMA 0 initial destination register 0x00000000

DIDST1 0x4B000048 R/W DMA 1 initial destination register 0x00000000

DIDST2 0x4B000088 R/W DMA 2 initial destination register 0x00000000

DIDST3 0x4B0000B8 R/W DMA 3 initial destination register 0x00000000

DIDSTn Bit Description Initial State

D_ADDR [30:0] Base address (start address) of destination for the transfer. This bit

value will be loaded into CURR_SRC only if the CURR_DST is 0 and the

DMA ACK is 1.

0x00000000

DMA INITIAL DESTINATION CONTROL (DIDSTC) REGISTER

Register Address R/W Description Reset Value

DIDSTC0 0x4B00000C R/W DMA 0 initial destination control register 0x00000000

DIDSTC1 0x4B00004C R/W DMA 1 initial destination control register 0x00000000

DIDSTC2 0x4B00008C R/W DMA 2 initial destination control register 0x00000000

DIDSTC3 0x4B0000CC R/W DMA 3 initial destination control register 0x00000000

DIDSTCn Bit Description Initial State

CHK_INT [2] Select interrupt occurrence time when auto reload is setting.

0 : Interrupt will occur when TC reaches 0.

1 : Interrupt will occur after auto-reload is performed.

0

LOC [1] Bit 1 is used to select the location of destination.

0: the destination is in the system bus (AHB).

1: the destination is in the peripheral bus (APB).

0

INC [0] Bit 0 is used to select the address increment.

0 = Increment 1= Fixed

If it is 0, the address is increased by its data size after each transfer in

burst and single transfer mode.

If it is 1, the address is not changed after the transfer. (In the burst

mode, address is increased during the burst transfer, but the address is

recovered to its first value after the transfer.)

0