THUMB INSTRUCTION SET S3C2440A RISC MICROPROCESSOR

4-4

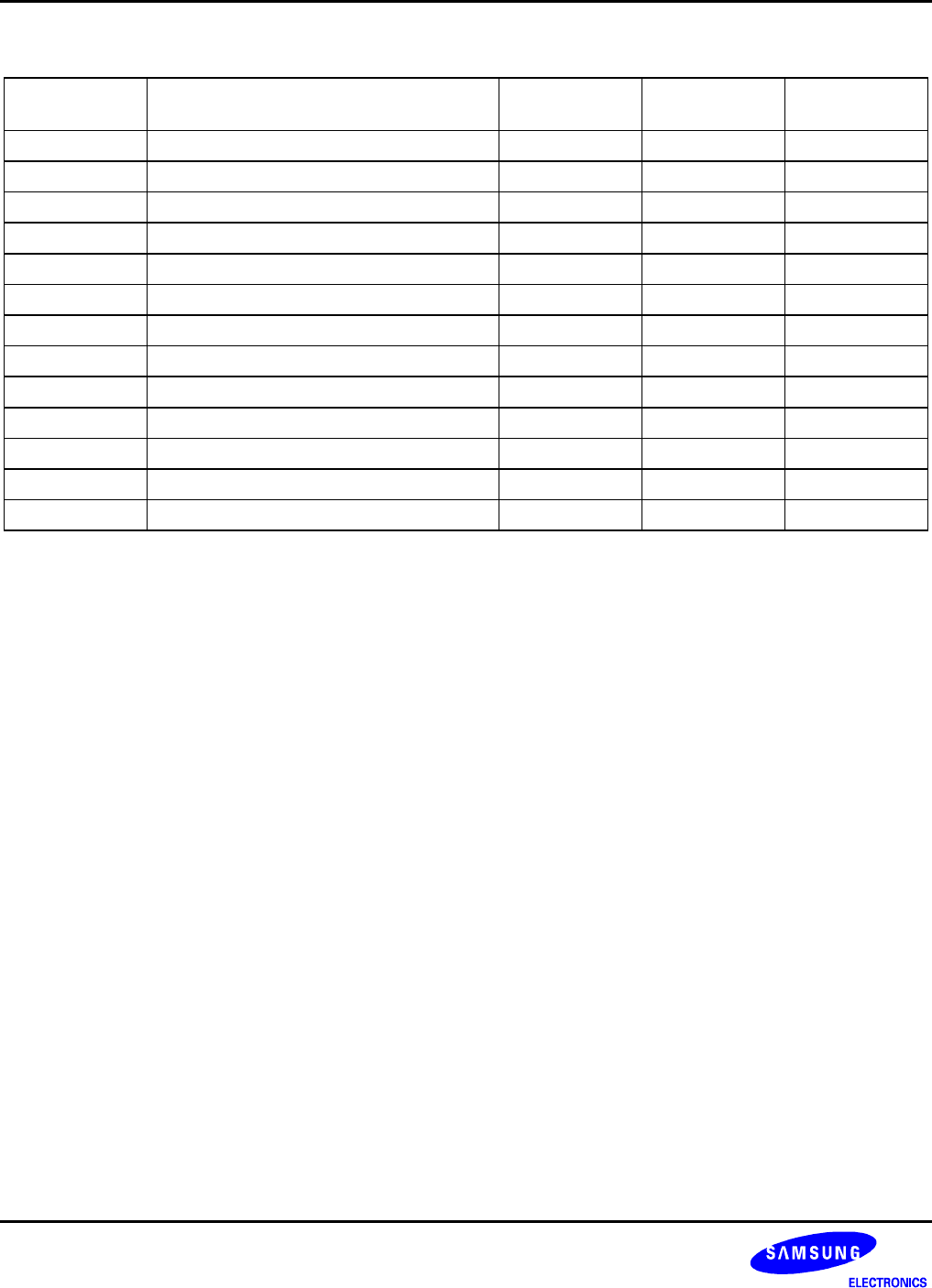

Table 4-1. THUMB Instruction Set Opcodes (Continued)

Mnemonic Instruction Lo-Register

Operand

Hi-Register

Operand

Condition

Codes Set

NEG Negate Y – Y

ORR OR Y – Y

POP Pop register Y – –

PUSH Push register Y – –

ROR Rotate Right Y – Y

SBC Subtract with Carry Y – Y

STMIA Store Multiple Y – –

STR Store word Y – –

STRB Store byte Y – –

STRH Store halfword Y – –

SWI Software Interrupt – – –

SUB Subtract Y – Y

TST Test bits Y – Y

NOTES

1. The condition codes are unaffected by the format 5, 12 and 13 versions of this instruction.

2. The condition codes are unaffected by the format 5 version of this instruction.