S3C2440A RISC MICROPROCESSOR I/O PORTS

9-31

EINTFLTn(External Interrupt Filter Register n)

To recognize the level interrupt, the valid logic level on EXTINTn pin must be retained for 40ns at least because of

the noise filter.

Register Address R/W Description Reset Value

EINTFLT0 0x56000094 R/W reserved 0x000000

EINTFLT1 0x56000098 R/W reserved 0x000000

EINTFLT2 0x5600009c R/W External Interrupt control Register 2 0x000000

EINTFLT3 0x4c6000a0 R/W External Interrupt control Register 3 0x000000

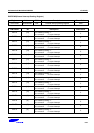

EINTFLT2 Bit Description

EINTFLT19 [30:24] Filtering width of EINT19

FLTCLK18 [23] Filter clock of EINT18(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT18 [22:16] Filtering width of EINT18

FLTCLK17 [15] Filter clock of EINT17(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT17 [14:8] Filtering width of EINT17

FLTCLK16 [7] Filter clock of EINT16(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT16 [6:0] Filtering width of EINT16

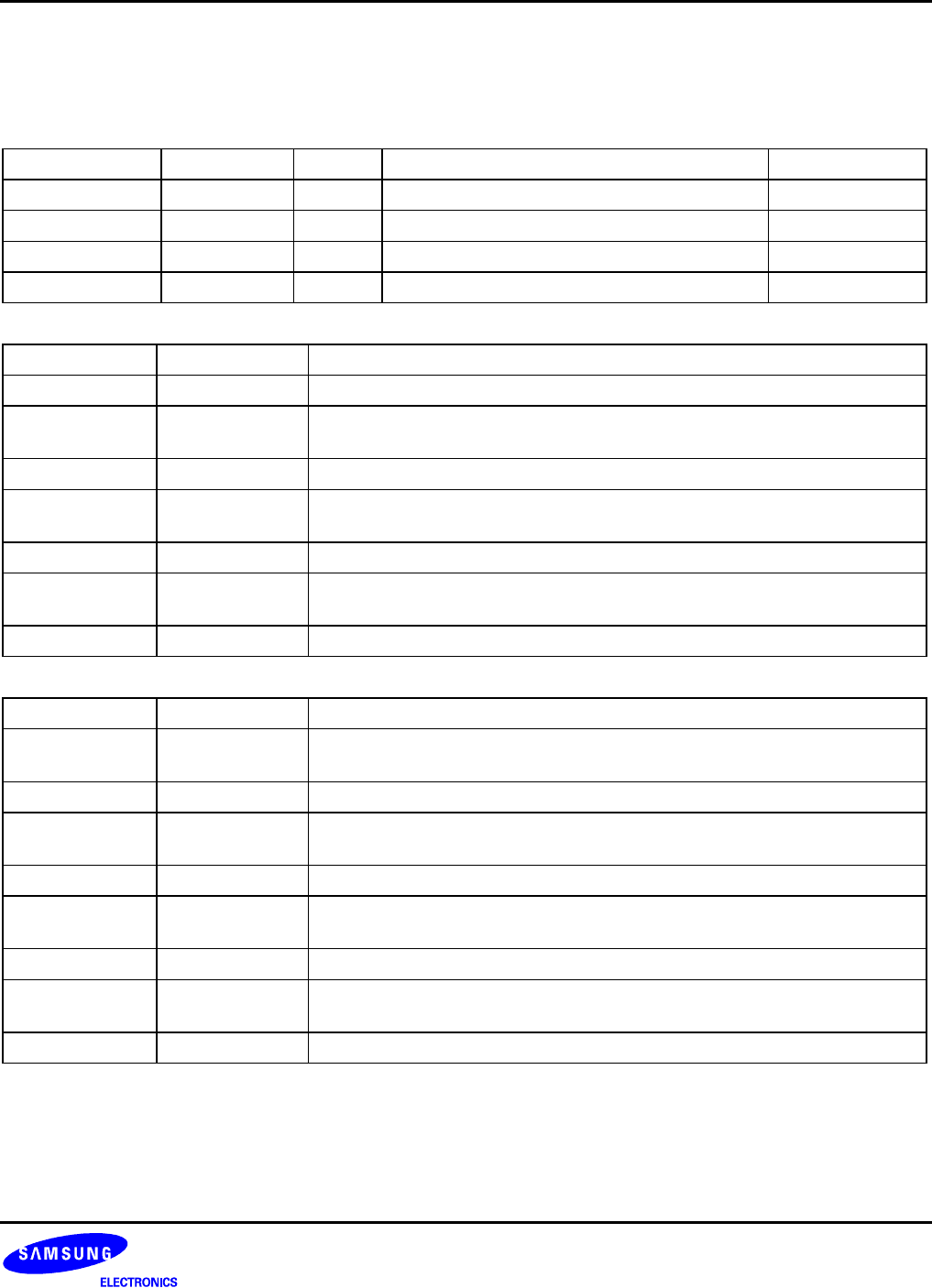

EINTFLT3 Bit Description

FLTCLK23 [31] Filter clock of EINT23(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT23 [30:24] Filtering width of EINT23

FLTCLK22 [23] Filter clock of EINT22(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT22 [22:16] Filtering width of EINT22

FLTCLK21 [15] Filter clock of EINT21(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT21 [14:8] Filtering width of EINT21

FLTCLK20 [7] Filter clock of EINT20(Configured by OM)

0 = PCLK 1= EXTCLK/OSC_CLK

EINTFLT20 [6:0] Filtering width of EINT20