S3C2440A RISC MICROPROCESSOR ELECTRICAL DATA

27-37

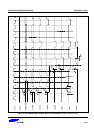

Table 27-8 ROM/SRAM Bus Timing Constants

(V

DDi,

V

DDalive,

V

DDiarm

= 1.2 V ± 0.1 V, T

A

= -40 to 85 °C, V

DDMOP

= 3.3V ± 0.3V / 3.0V ± 0.3V / 2.5V ± 0.2V / 1.8V

± 0.1V)

Parameter Symbol

Min

(V

DDMOP

=

3.3V/3.0V/2.5V/1.8V)

Typ

Max

(V

DDMOP

=

3.3V/3.0V/2.5V/1.8V)

Unit

ROM/SRAM Address Delay

t

RAD

2 / 2 / 2 / 3 – 6 / 6 / 7 / 8 ns

ROM/SRAM Chip Select Delay

t

RCD

2 / 2 / 3 / 3 – 6 / 6 / 6 / 7 ns

ROM/SRAM Output Enable Delay

t

ROD

2 / 2 / 2 / 3 – 5 / 5 / 5 / 6 ns

ROM/SRAM Read Data Setup Time.

t

RDS

1 / 1 / 1 / 2 – – / – / – / – ns

ROM/SRAM Read Data Hold Time.

t

RDH

0 / 0 / 0 / 0 – – / – / – / – ns

ROM/SRAM Byte Enable Delay

t

RBED

2 / 2 / 2 / 3 – 5 / 5 / 5 / 7 ns

ROM/SRAM Write Byte Enable Delay

t

RWBED

2 / 2 / 2 / 3 – 5 / 5 / 6 / 7 ns

ROM/SRAM Output Data Delay

t

RDD

2 / 2 / 2 / 2 – 6 / 6 / 6 / 7 ns

ROM/SRAM External Wait Setup Time

t

WS

3 / 3 / 4 / 4 – – / – / – / – ns

ROM/SRAM External Wait Hold Time

t

WH

0 / 0 / 0 / 0 – – / – / – / – ns

ROM/SRAM Write Enable Delay

t

RWD

2 / 2 / 2 / 3 – 5 / 5 / 6 / 7 ns

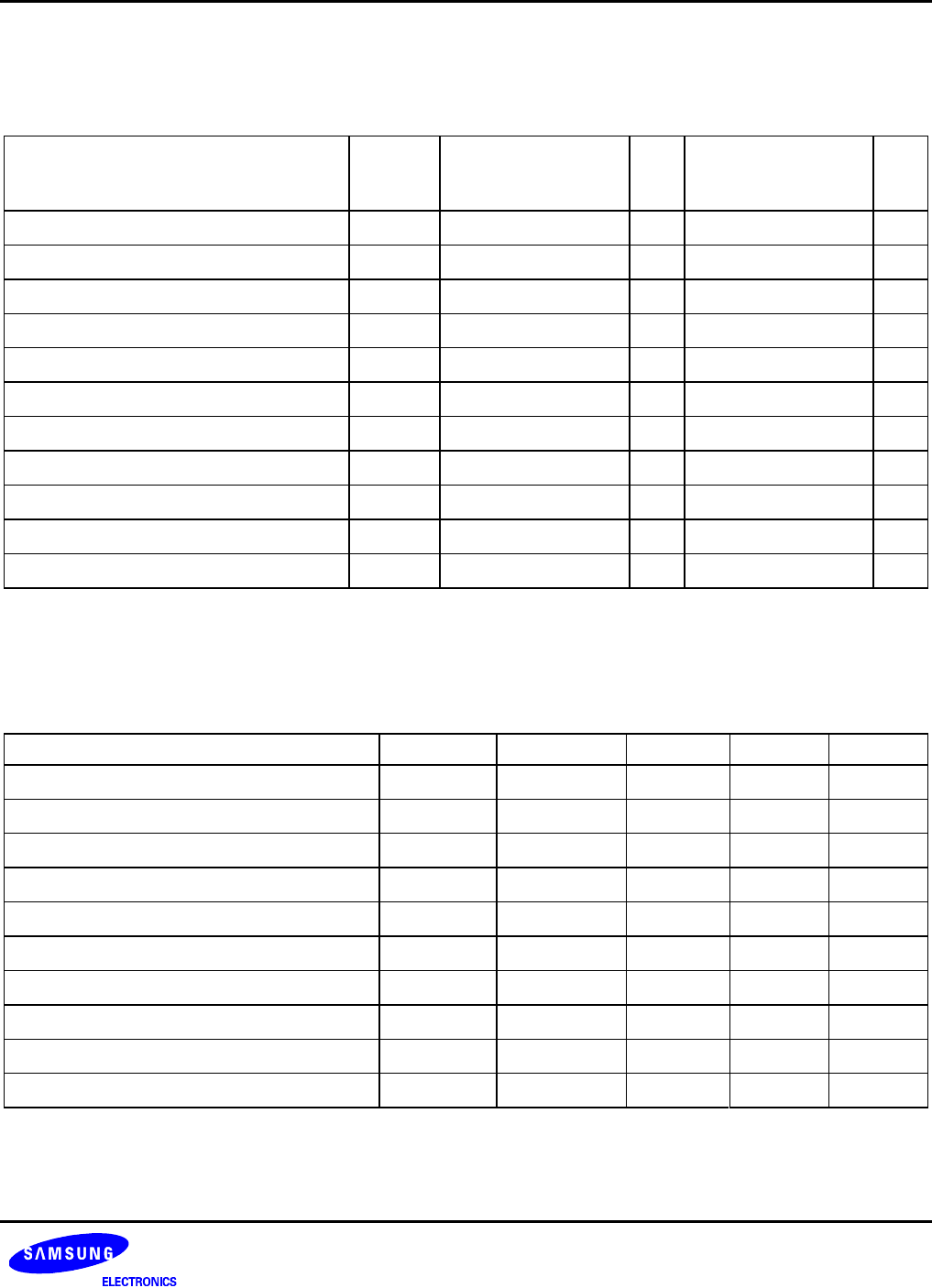

Table 27-9 Memory Interface Timing Constants

(V

DDi,

V

DDalive,

V

DDiarm

= 1.2 V ± 0.1 V, T

A

= -40 to 85 °C, V

DDMOP

= 3.3V ± 0.3V / 3.0V ± 0.3V / 2.5V ± 0.2V / 1.8V

± 0.1V)

Parameter Symbol Min Typ Max Unit

SDRAM Address Delay

t

SAD

1 – 4 ns

SDRAM Chip Select Delay

t

SCSD

1 – 3 ns

SDRAM Row Active Delay

t

SRD

1 – 3 ns

SDRAM Column Active Delay

t

SCD

1 – 3 ns

SDRAM Byte Enable Delay

t

SBED

1 – 3 ns

SDRAM Write Enable Delay

t

SWD

1 – 2 ns

SDRAM Read Data Setup Time

t

SDS

2 / 3 / 3 / 5 * – – ns

SDRAM Read Data Hold Time

t

SDH

0 – – ns

SDRAM Output Data Delay

t

SDD

1 – 4 ns

SDRAM Clock Enable Delay

T

cked

2 – 3 ns

NOTE: Minimum t

SDS

= 2ns / 3ns / 3ns, when V

DDMOP

= 3.3V / 3.0V / 2.5V / 1.8V respectively.