MMC/SD/SDIO CONTROLLER S3C2440A RISC MICROPROCESSOR

19-10

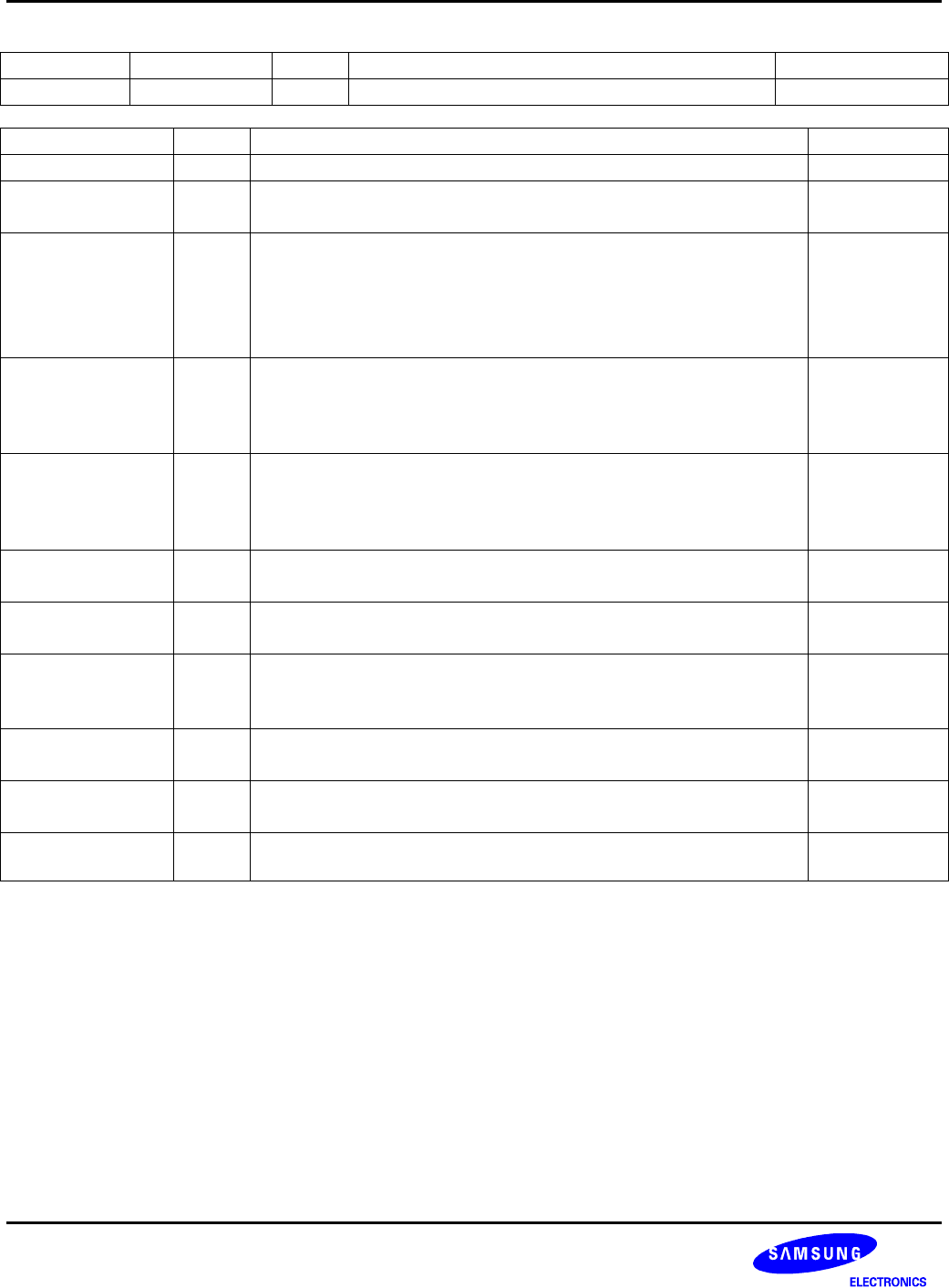

SDI FIFO Status Register(SDIFSTA)

Register Address R/W Description Reset Value

SDIFSTA 0x5A000038 R/(C) SDI FIFO Status Register 0x0

SDIFSTA Bit Description Initial State

Reserved [31:16]

FIFO Reset(FRST) [16]

C

Reset FIFO value. This bit is automatically cleared.

0 = normal mode, 1 = FIFO reset

0

FIFO Fail error

(FFfail)

[15:14]

R/C

FIFO fail error when FIFO occurs overrun / underrun data saving.

This flag is cleared by setting to one these bits.

00 = not detect, 01 = FIFO fail

10 = FIFO fail in the last transfer(only FIFO reset need)

11 = reserved

0

FIFO available

Detect for Tx

(TFDET)

[13] This bit indicates that FIFO data is available for transmit when

DatMode is data transmit mode. If DMA mode is enable, sd host

requests DMA operation.

0 = not detect(FIFO full), 1 = detect(0 ≤ FIFO ≤ 63)

0

FIFO available

Detect for Rx

(RFDET)

[12] This bit indicates that FIFO data is available for receive when

DatMode is data receive mode. If DMA mode is enable, sd host

requests DMA operation.

0 = not detect(FIFO empty), 1 = detect(1 ≤ FIFO ≤ 64)

0

Tx FIFO Half Full

(TFHalf)

[11] This bit sets to 1 whenever Tx FIFO is less than 33byte.

0 = 33 ≤ Tx FIFO ≤ 64, 1 = 0 ≤ Tx FIFO ≤ 32

0

Tx FIFO Empty

(TFEmpty)

[10] This bit sets to 1 whenever Tx FIFO is empty.

0 = 1 ≤ Tx FIFO ≤ 64, 1 = Empty(0byte)

0

Rx FIFO Last Data

Ready (RFLast)

[9]

R/C

This bit sets to 1 when Rx FIFO occurs to behave last data of all

block. This flag is cleared by setting to one this bit.

0 = not received yet, 1 = Rx FIFO gets Last data

0

Rx FIFO Full

(RFFull)

[8] This bit sets to 1 whenever Rx FIFO is full.

0 = 0 ≤ Rx FIFO ≤ 63, 1 = Full(64byte)

0

Rx FIFO Half Full

(RFHalf)

[7] This bit sets to 1 whenever Rx FIFO is more than 31byte.

0 = 0 ≤ Rx FIFO ≤ 31, 1 = 32 ≤ Rx FIFO ≤ 64

0

FIFO Count

(FFCNT)

[6:0] Number of data(byte) in FIFO 0000000

* Although the last Rx data size is lager than remained count of FIFO data, you could read this data. If this

event happens, you should clear FFfail field, and FIFO reset field