ARM INSTRUCTION SET S3C2440A RISC MICROPROCESSOR

3-10

The instruction produces a result by performing a specified arithmetic or logical operation on one or two operands.

The first operand is always a register (Rn).

The second operand may be a shifted register (Rm) or a rotated 8 bit immediate value (Imm) according to the

value of the I bit in the instruction. The condition codes in the CPSR may be preserved or updated as a result of

this instruction, according to the value of the S bit in the instruction.

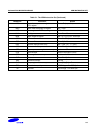

Certain operations (TST, TEQ, CMP, CMN) do not write the result to Rd. They are used only to perform tests and

to set the condition codes on the result and always have the S bit set. The instructions and their effects are listed in

Table 3-3.