S3C2440A RISC MICROPROCESSOR CLOCK & POWER MANAGEMENT

7-13

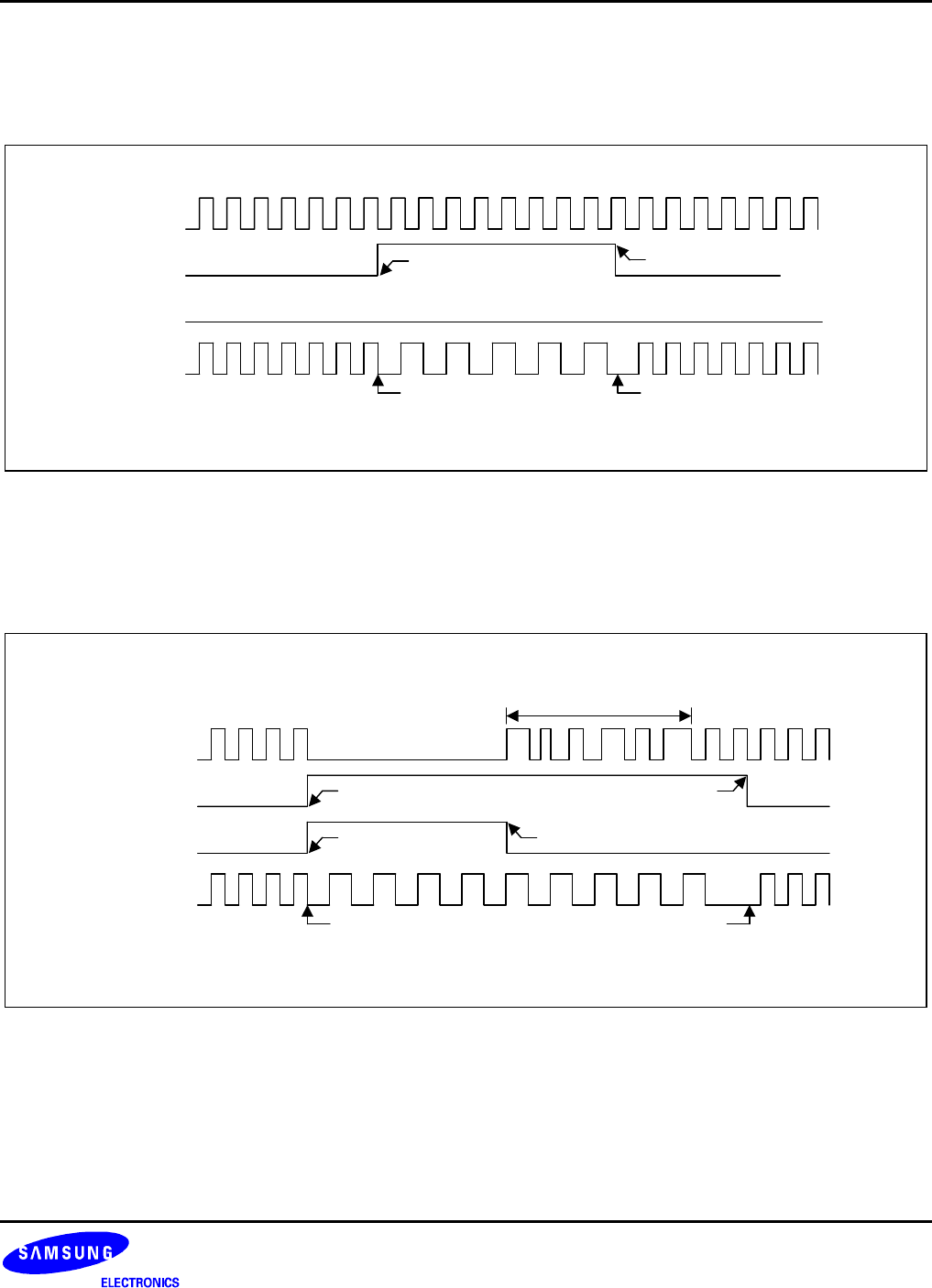

Users can change the frequency by enabling SLOW mode bit in CLKSLOW register in PLL on state. The SLOW

clock is generated during the SLOW mode. Figure 7-11(Please check the figure correctly) shows the timing

diagram.

Mpll

Slow mode disable

FCLK

Slow mode enable

SLOW_BIT

Divided external clock

MPLL_OFF

It changes to PLL clock

after slow mode off

Figure 7-9. Issuing Exit_from_Slow_mode Command in PLL on State

If the user switches from SLOW mode to Normal mode by disabling the SLOW_BIT in the CLKSLOW register

after PLL lock time, the frequency is changed just after SLOW mode is disabled. Figure 7-12 (Please check for the

figure number correctly) shows the timing diagram.

Mpll

FCLK

SLOW_BIT

Divided OSC clock

MPLL_OFF

Software lock time

Slow mode disable

PLL off PLL on

Slow mode enable

It changes to PLL clock

after slow mode off

Figure 7-10. Issuing Exit_from_Slow_mode Command After Lock Time