DMA S3C2440A RISC MICROPROCESSOR

8-4

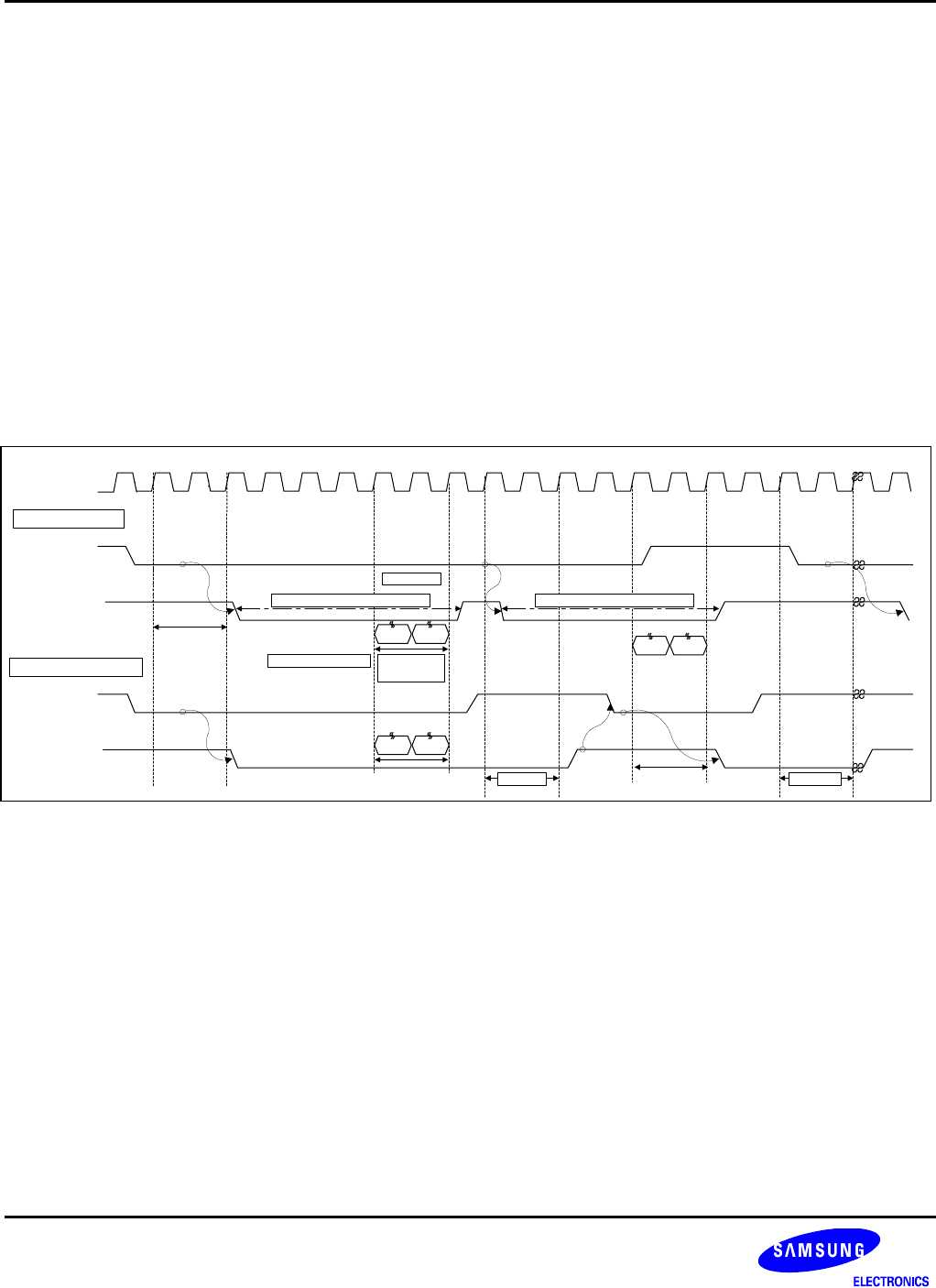

Demand/Handshake Mode Comparison

Demand and Handshake modes are related to the protocol between XnXDREQ and XnXDACK. Figure 8-2 shows

the differences between the two modes.

At the end of one transfer (Single/Burst transfer), DMA checks the state of double-synched XnXDREQ.

Demand mode

- If XnXDREQ remains asserted, the next transfer starts immediately. Otherwise it waits for XnXDREQ to

be asserted.

Handshake mode

- If XnXDREQ is de-asserted, DMA de-asserts XnXDACK in 2cycles. Otherwise it waits until XnXDREQ is

de-asserted.

Caution: XnXDREQ has to be asserted (low) only after the de-assertion (high) of XnXDACK.

Demand Mode

XSCLK

XnXDACK

XnXDACK

XnXDREQ

XnXDREQ

2cycles

Double

synch

Read Write

Read Write

Handshake Mode

BUS Acquisiton

Actual

Transfer

1st Transfer 2nd Transfer

2cycles

Read Write

Double

synch

2cycles

Figure 8-2. Demand/Handshake Mode Comparison