PWM TIMER S3C2440A RISC MICROPROCESSOR

10-10

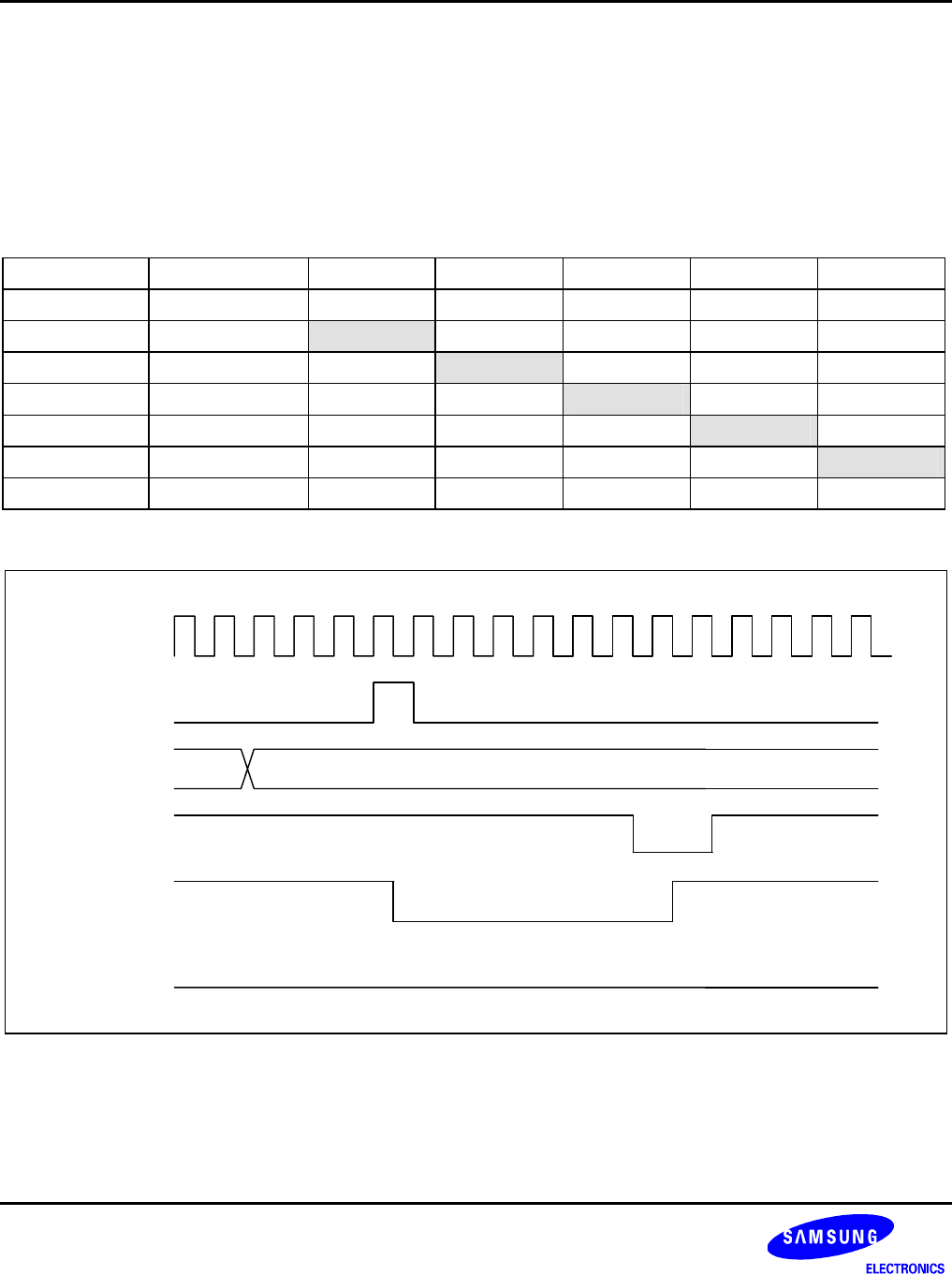

DMA REQUEST MODE

The PWM timer can generate a DMA request at every specific time. The timer keeps DMA request signals

(nDMA_REQ) low until the timer receives an ACK signal. When the timer receives the ACK signal, it makes the

request signal inactive. The timer, which generates the DMA request, is determined by setting DMA mode bits (in

TCFG1 register). If one of timers is configured as DMA request mode, that timer does not generate an interrupt

request. The others can generate interrupt normally.

DMA mode configuration and DMA / interrupt operation

DMA Mode DMA Request Timer0 INT Timer1 INT Timer2 INT Timer3 INT Timer4 INT

0000 No select ON ON ON ON ON

0001 Timer0 OFF ON ON ON ON

0010 Timer1 ON OFF ON ON ON

0011 Timer2 ON ON OFF ON ON

0100 Timer3 ON ON ON OFF ON

0101 Timer4 ON ON ON ON OFF

0110 No select ON ON ON ON ON

PCLK

INT4tmp

DMAreq_en

nDMA_ACK

nDMA_REQ

INT4

1 0 1

Figure 10-8. Timer4 DMA Mode Operation