S3C2440A RISC MICROPROCESSOR CLOCK & POWER MANAGEMENT

7-25

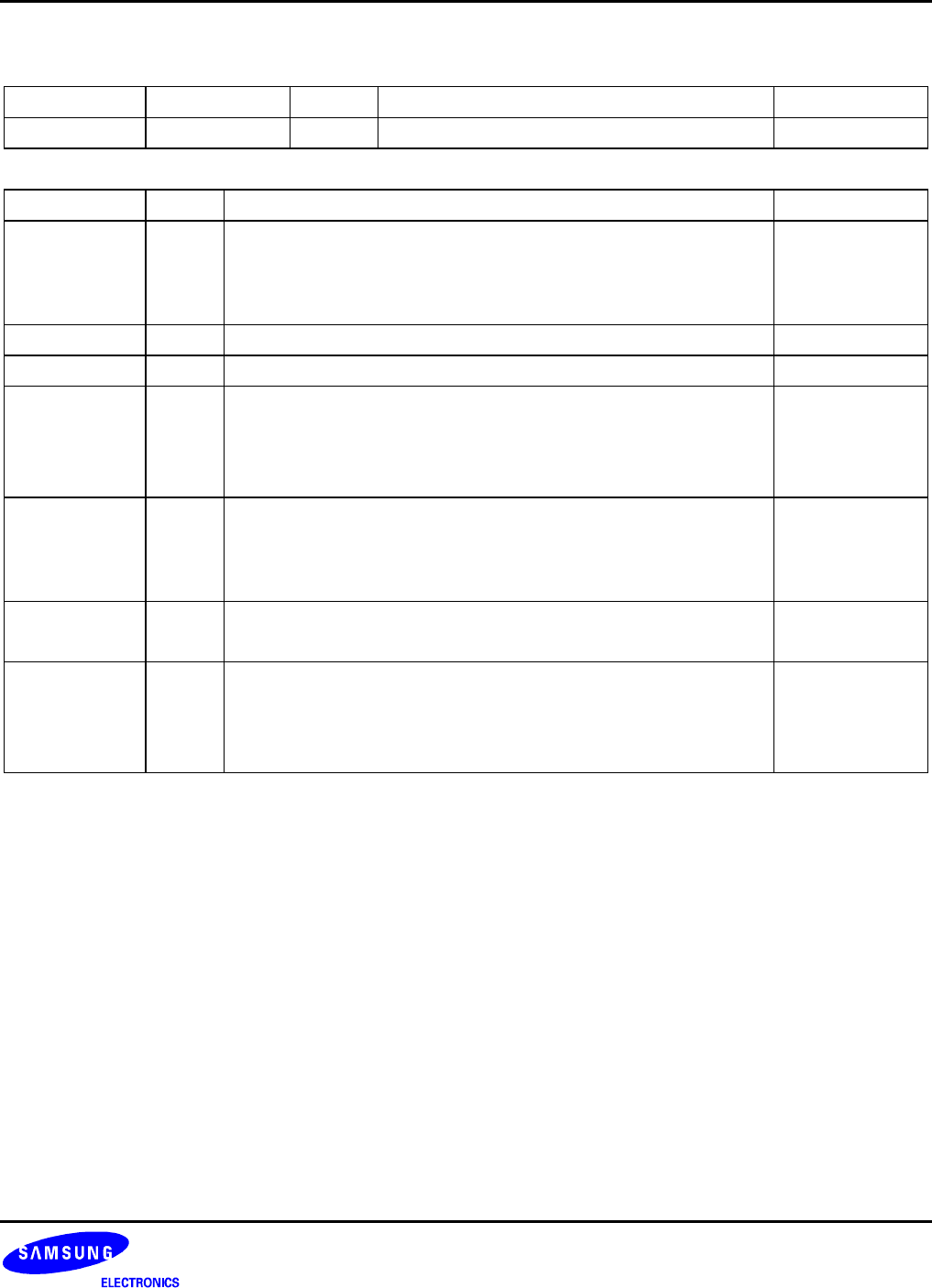

CAMERA CLOCK DIVIDER (CAMDIVN) REGISTER

Register Address R/W Description Reset Value

CAMDIVN 0x4C000018 R/W Camera clock divider register 0x00000000

CAMDIVN Bit Description Initial State

DVS_EN [12] 0:DVS OFF

ARM core will run normally with FCLK(MPLLout).

1:DVS ON

ARM core will run at the same clock as system clock(HCLK).

0

Reserved [11] 0

Reserved [10] 0

HCLK4_HALF [9] HDIVN division rate change bit, when CLKDIVN[2:1]=10b.

0: HCLK = FCLK/4 1: HCLK= FCLK/8

Refer the CLKDIV register.

0

HCLK3_HALF [8]

HDIVN division rate change bit, when CLKDIVN[2:1]=11b.

0: HCLK = FCLK/3 1: HCLK= FCLK/6

Refer the CLKDIV register.

0

CAMCLK_SEL [4] 0:Use CAMCLK with UPLL output(CAMCLK=UPLL output).

1:CAMCLK is divided by CAMCLK_DIV value.

0

CAMCLK_DIV [3:0] CAMCLK divide factor setting register(0 – 15).

Camera clock = UPLL / [(CAMCLK_DIV +1)x2].

This bit is valid when CAMCLK_SEL=1.

0