S3C2440A RISC MICROPROCESSOR USB DEVICE

13-3

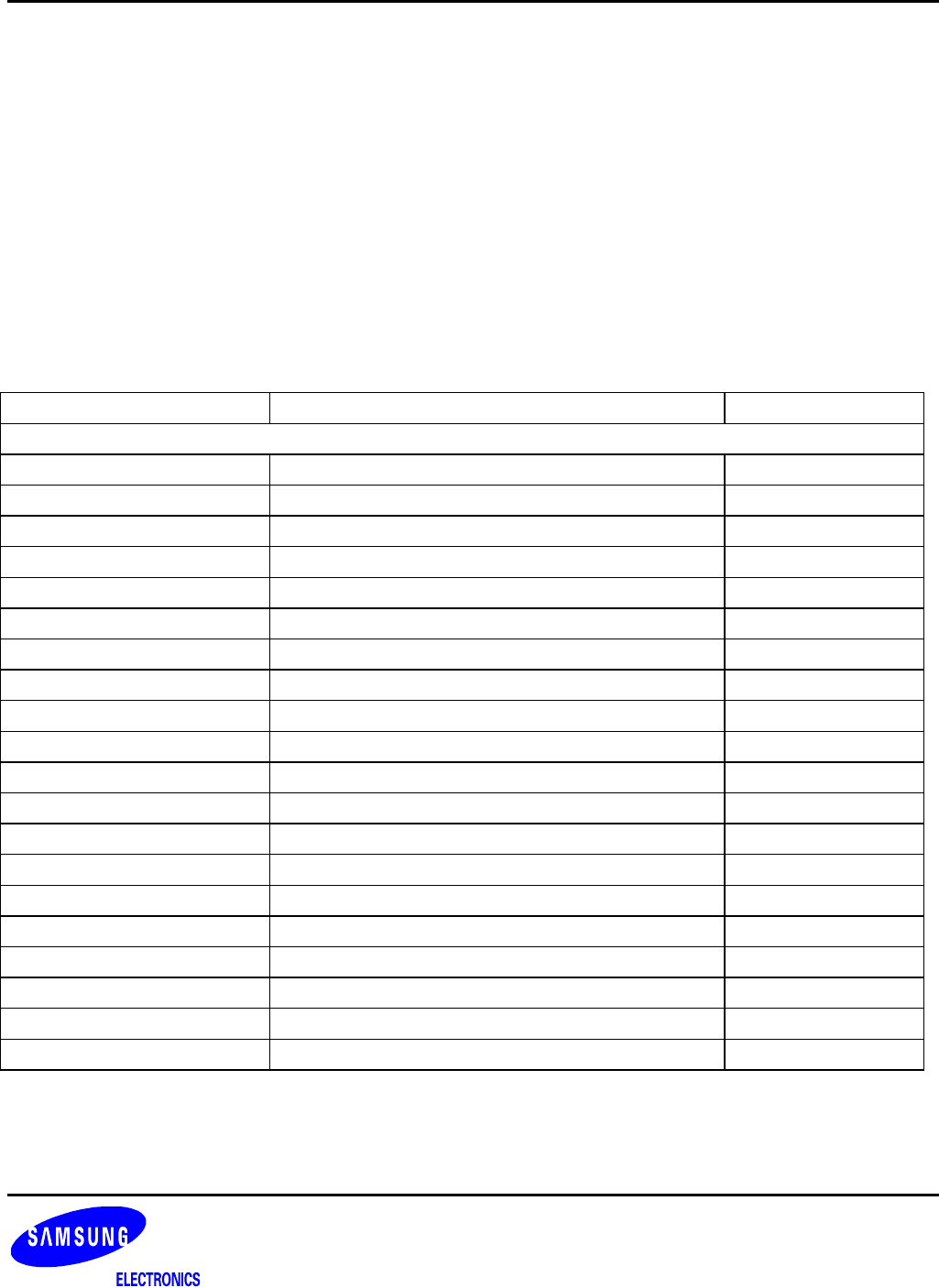

USB DEVICE CONTROLLER SPECIAL REGISTERS

This section describes detailed functionalities about register sets of USB device controller.

All special function register is byte-accessible or word-accessible. If you access byte mode offset-address is

different in little endian and big endian. All reserved bit is zero.

Common indexed registers depend on INDEX register (INDEX_REG) (offset address: 0X178) value. For example

if you want to write EP0 CSR register, you must write ‘0x00’ on the INDEX_REG before writing IN_CSR1 register.

NOTE

All register must be resettled after performing Host Reset Signaling.

Register Name Description Offset Address

NON INDEXED REGISTERS

FUNC_ADDR_REG Function address register 0x140(L) / 0x143(B)

PWR_REG Power management register 0x144(L) / 0x147(B)

EP_INT_REG (EP0–EP4) Endpoint interrupt register 0x148(L) / 0x14B(B)

USB_INT_REG USB interrupt register 0x158(L) / 0x15B(B)

EP_INT_EN_REG (EP0–EP4) Endpoint interrupt enable register 0x15C(L) / 0x15F(B)

USB_INT_EN_REG USB Interrupt enable register 0x16C(L) / 0x16F(B)

FRAME_NUM1_REG Frame number 1 register 0x170(L) / 0x173(B)

FRAME_NUM2_REG Frame number 2 register 0x174(L) / 0x177(B)

INDEX_REG Index register 0x178(L) / 0x17B(B)

EP0_FIFO_REG Endpoint0 FIFO register 0x1C0(L) / 0x1C3(B)

EP1_FIFO_REG Endpoint1 FIFO register 0x1C4(L) / 0x1C7(B)

EP2_FIFO_REG Endpoint2 FIFO register 0x1C8(L) / 0x1CB(B)

EP3_FIFO_REG Endpoint3 FIFO register 0x1CC(L) / 0x1CF(B)

EP4_FIFO_REG Endpoint4 FIFO register 0x1D0(L) / 0x1D3(B)

EP1_DMA_CON Endpoint1 DMA control register 0x200(L) / 0x203(B)

EP1_DMA_UNIT Endpoint1 DMA unit counter register 0x204(L) / 0x207(B)

EP1_DMA_FIFO Endpoint1 DMA FIFO counter register 0x208(L) / 0x20B(B)

EP1_DMA_TTC_L Endpoint1 DMA transfer counter low-byte register 0x20C(L) / 0x20F(B)

EP1_DMA_TTC_M Endpoint1 DMA transfer counter middle-byte register 0x210(L) / 0x213(B)

EP1_DMA_TTC_H Endpoint1 DMA transfer counter high-byte register 0x214(L) / 0x217(B)