NAND FLASH CONTROLLER S3C2440A RISC MICROPROCESSOR

6-2

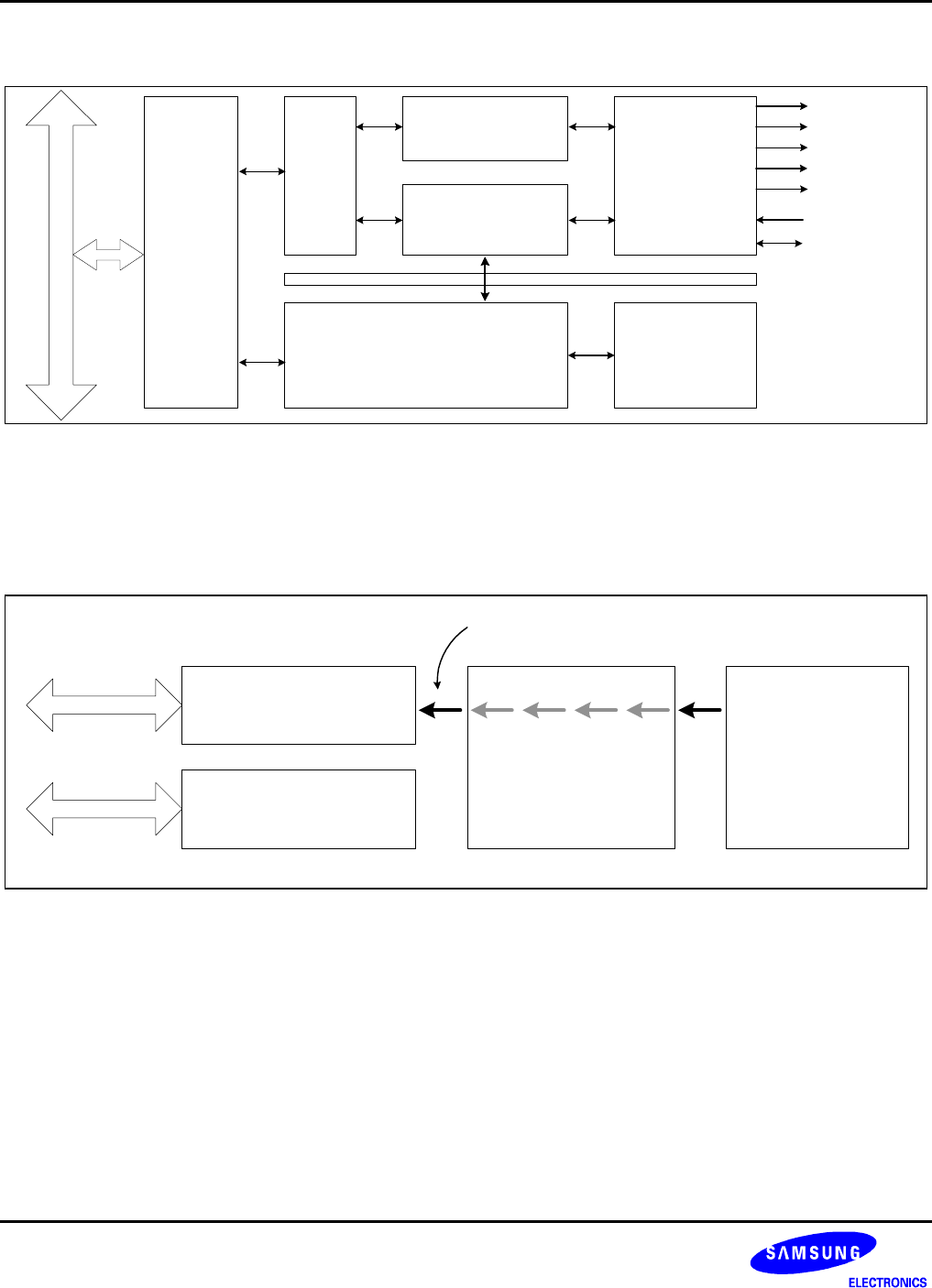

BLOCK DIAGRAM

zmy

ljjGnU

zGz

O[riGzyhtP

zGz

j

SYSTEM BUS

uhukGmshzo

p

CLE

ALE

nFCE

nFRE

nFWE

FRnB

I/O0 - I/O15

hoi

zGpVm

jGM

zGt

Figure 6-1 NAND Flash Controller Block Diagram

BOOT LOADER FUNCTION

zGz

O[riGiP

uhukGmshzo

j

uhukGmshzo

t

zGm

y

REGISTERS

AUTO BOOT

CORE ACCESS

(Boot Code)

USER ACCESS

Figure 6-2 NAND Flash Controller Boot Loader Block Diagram

During reset, Nand flash controller will get information about the connected NAND flash through Pin status

(NCON(Adv flash), GPG13(Page size), GPG14(Address cycle), GPG15(Bus width) – refer to PIN

CONFIGURATION), After power-on or system reset is occurred, the NAND Flash controller load automatically the

4-KBytes boot loader codes. After loading the boot loader codes, the boot loader code in steppingstone is

executed.

NOTE

During the auto boot, the ECC is not checked. So, the first 4-KB of NAND flash should have no bit error.