S3C2440A RISC MICROPROCESSOR IIC-BUS INTERFACE

20-3

IIC-BUS INTERFACE

The S3C2440A IIC-bus interface has four operation modes:

— Master transmitter mode

— Master receive mode

— Slave transmitter mode

— Slave receive mode

Functional relationships among these operating modes are described below.

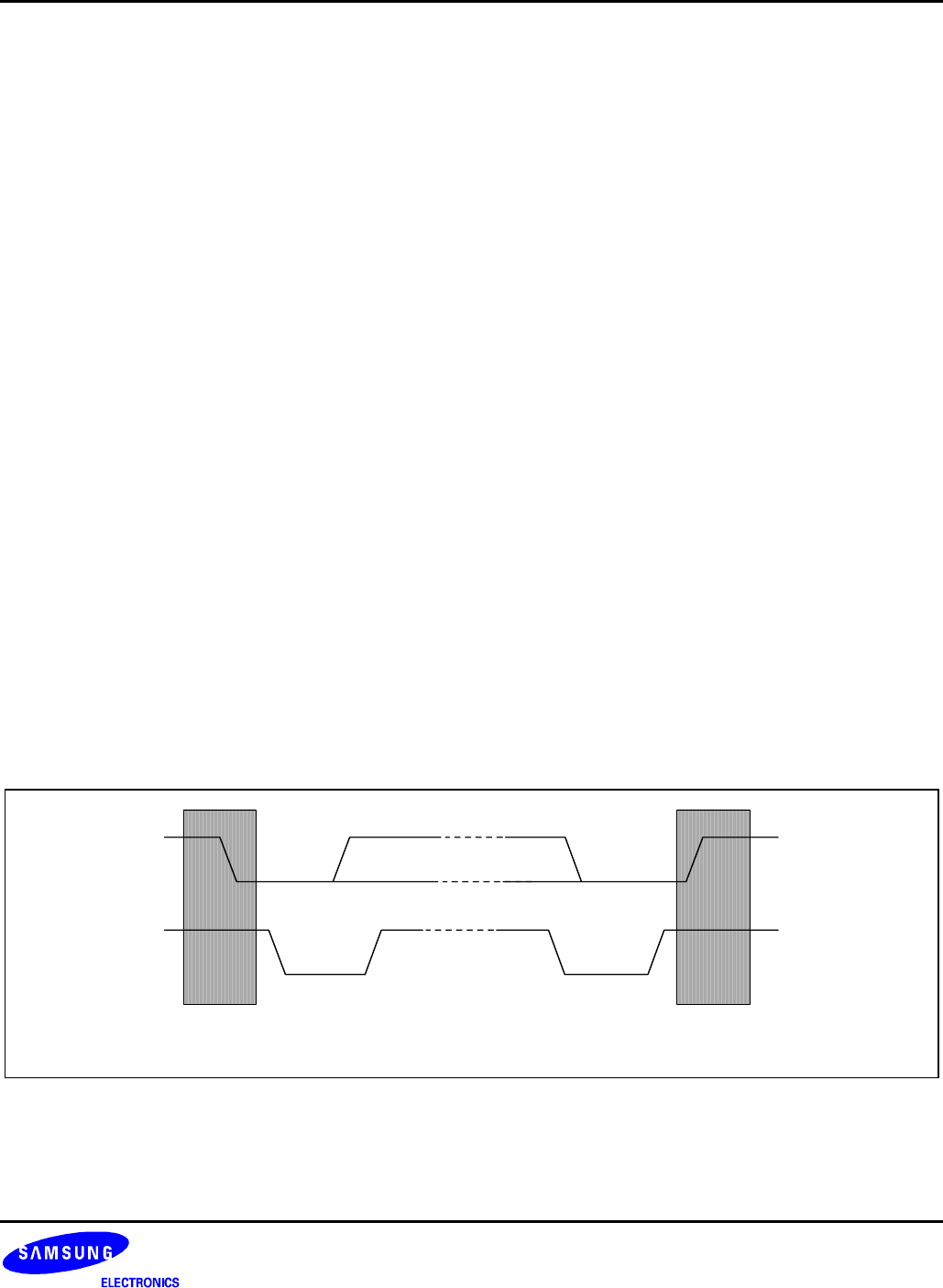

START AND STOP CONDITIONS

When the IIC-bus interface is inactive, it is usually in Slave mode. In other words, the interface should be in Slave

mode before detecting a Start condition on the SDA line (a Start condition can be initiated with a High-to-Low

transition of the SDA line while the clock signal of SCL is High). When the interface state is changed to Master

mode, a data transfer on the SDA line can be initiated and SCL signal generated.

A Start condition can transfer a one-byte serial data over the SDA line, and a Stop condition can terminate the data

transfer. A Stop condition is a Low-to-High transition of the SDA line while SCL is High. Start and Stop conditions

are always generated by the master. The IIC-bus gets busy when a Start condition is generated. A Stop condition

will make the IIC-bus free.

When a master initiates a Start condition, it should send a slave address to notify the slave device. One byte of

address field consists of a 7-bit address and a 1-bit transfer direction indicator (showing write or read).

If bit 8 is 0, it indicates a write operation (transmit operation); if bit 8 is 1, it indicates a request for data read (receive

operation).

The master will complete the transfer operation by transmitting a Stop condition. If the master wants to continue the

data transmission to the bus, it should generate another Start condition as well as a slave address. In this way, the

read-write operation can be performed in various formats.

SCL

SDA SDA

SCL

Start

Condition

Stop

Condition

Figure 20-2. Start and Stop Condition