IIC-BUS INTERFACE S3C2440A RISC MICROPROCESSOR

20-14

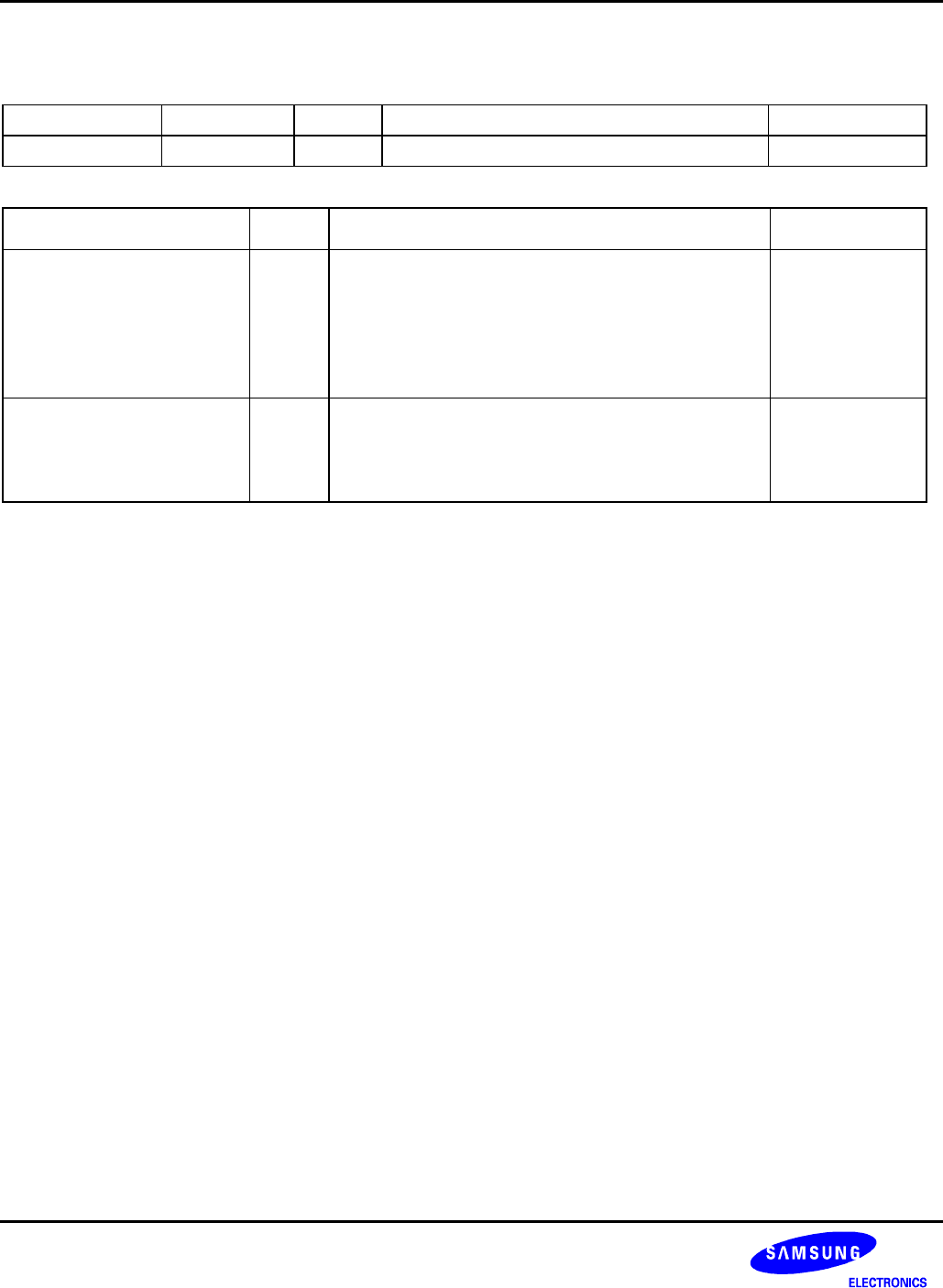

MULTI-MASTER IIC-BUS LINE CONTROL(IICLC) REGISTER

Register Address R/W Description Reset Value

IICLC 0x54000010 R/W IIC-Bus multi-master line control register 0x00

IICLC Bit Description Initial State

Filter Enable [2] IIC-bus filter enable bit.

When SDA port is operating as input, this bit should

be High. This filter can prevent from occurred error

by a glitch during double of PCLK time.

0 : Filter disable

1 : Filter enable

0

SDA output delay

[1:0] IIC-Bus SDA line delay length selection bits.

SDA line is delayed as following clock time(PCLK)

00 : 0 clocks 01 : 5 clocks

10 : 10 clocks 11 : 15 clocks

00