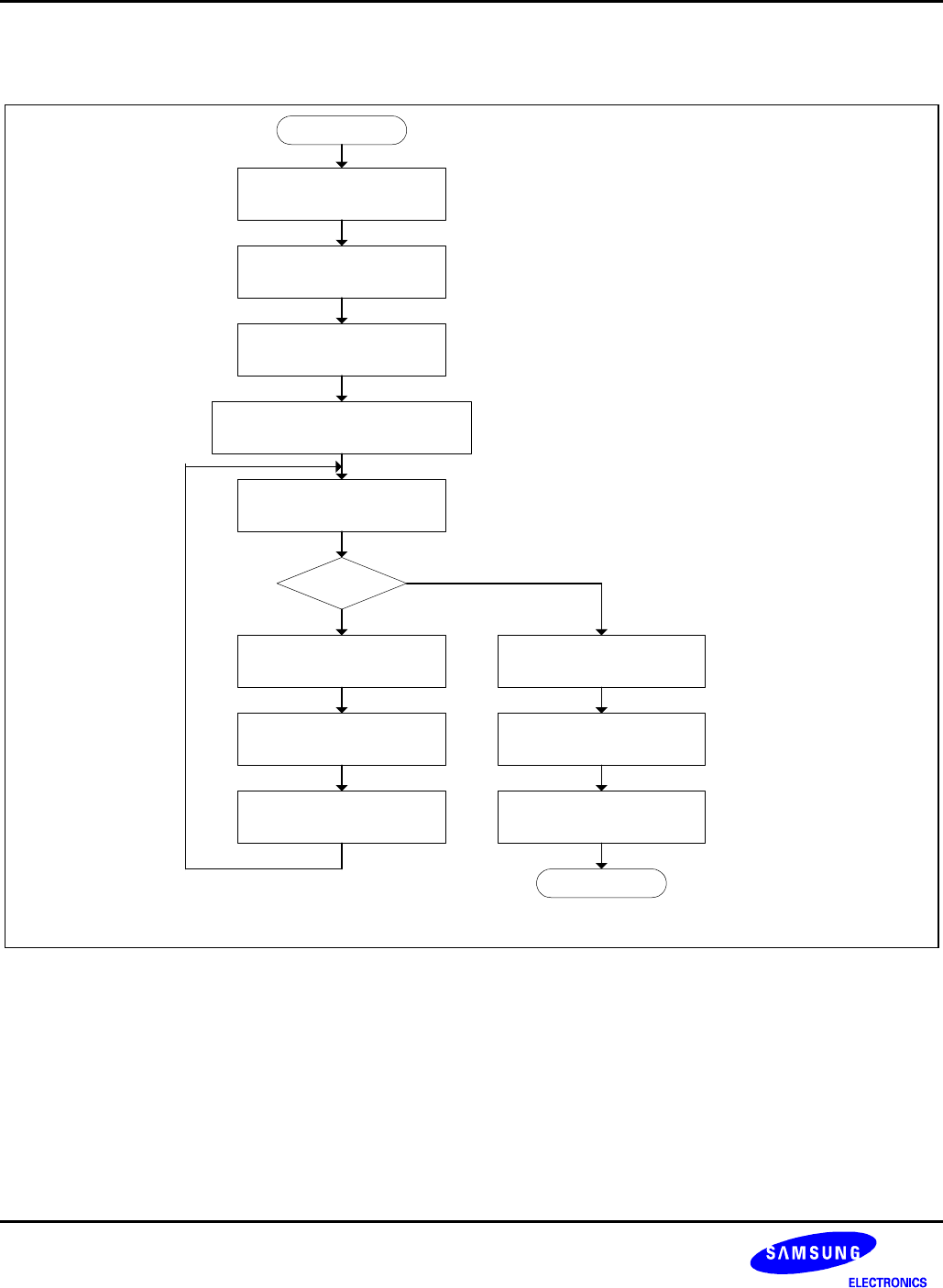

IIC-BUS INTERFACE S3C2440A RISC MICROPROCESSOR

20-8

Write slave address to

IICDS.

Write 0xB0 (M/R Start)

to IICSTAT.

The data of the IICDS (slave

address) is transmitted.

ACK period and then

interrupt is pending.

Write 0x90 (M/R Stop)

to IICSTAT.

Read a new data from

IICDS.

Stop?

Clear pending bit to

resume.

SDA is shifted to IICDS.

START

Master Rx mode has

been configured.

Clear pending bit .

Wait until the stop

condition takes effect.

END

Y

N

Figure 20-7 Operations for Master/Receiver Mode