CLOCK & POWER MANAGEMENT S3C2440A RISC MICROPROCESSOR

7-8

FCLK, HCLK, and PCLK

FCLK is used by ARM920T.

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the

LCD controller, the DMA and USB host block.

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,

ADC, UART, GPIO, RTC and SPI.

The S3C2440A supports selection of Dividing Ratio between FCLK, HLCK and PCLK. This ratio is determined by

HDIVN and PDIVN of CLKDIVN control register.

HDIVN PDIVN HCLK3_HALF/

HCLK4_HALF

FCLK HCLK PCLK Divide Ratio

0 0 - FCLK FCLK FCLK 1 : 1 : 1

(Default)

0 1 - FCLK FCLK FCLK / 2 1 : 1 : 2

1 0 - FCLK FCLK / 2 FCLK / 2 1 : 2 : 2

1 1 - FCLK FCLK / 2 FCLK / 4 1 : 2 : 4

3 0 0 / 0 FCLK FCLK / 3 FCLK / 3 1 : 3 : 3

3 1 0 / 0 FCLK FCLK / 3 FCLK / 6 1 : 3 : 6

3 0 1 / 0 FCLK FCLK / 6 FCLK / 6 1 : 6 : 6

3 1 1 / 0 FCLK FCLK / 6 FCLK / 12 1 : 6 : 12

2 0 0 / 0 FCLK FCLK / 4 FCLK / 4 1 : 4 : 4

2 1 0 / 0 FCLK FCLK / 4 FCLK / 8 1 : 4 : 8

2 0 0 / 1 FCLK FCLK / 8 FCLK / 8 1 : 8 : 8

2 1 0 / 1 FCLK FCLK / 8 FCLK / 16 1 : 8 : 16

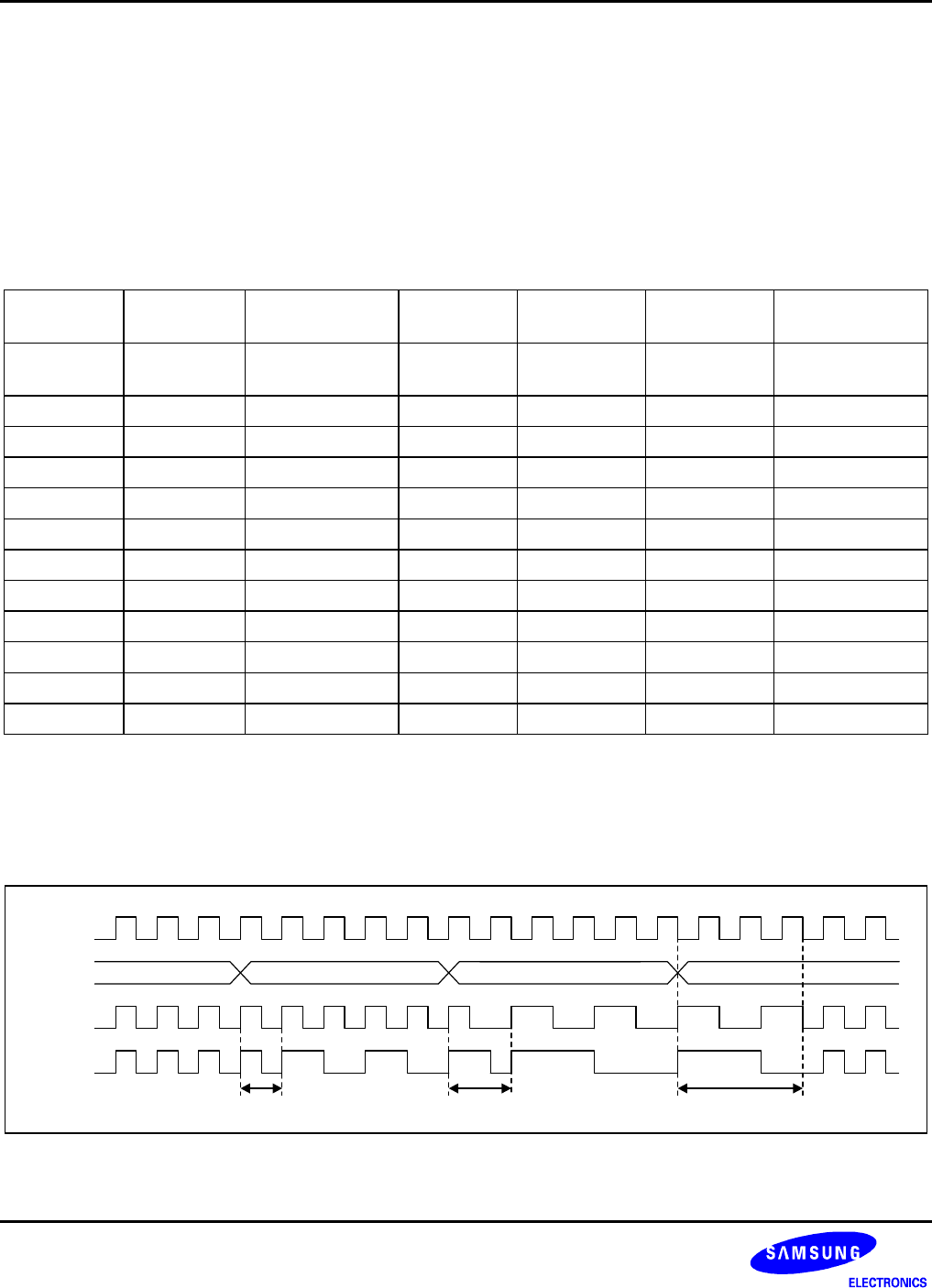

After setting PMS value, it is required to set CLKDIVN register. The value set for CLKDIVN will be valid after PLL

lock time. The value is also available for reset and changing Power Management Mode.

The setting value can also be valid after 1.5 HCLK. Only, 1HCLK can validate the value of CLKDIVN register

changed from Default (1:1:1) to other Divide Ratio (1:1:2, 1:2:2, 1:2:4).

1 HCLK 1.5 HCLK 1.5 HCLK

0x00000000 0x00000001(1:1:2) 0x00000003 (1:2:4) 0x00000000 (1:1:1)

CLKDIVN

FCLK

HCLK

PCLK

Figure 7-6. Example of internal clock change