ARM INSTRUCTION SET S3C2440A RISC MICROPROCESSOR

3-22

MULTIPLY AND MULTIPLY-ACCUMULATE (MUL, MLA)

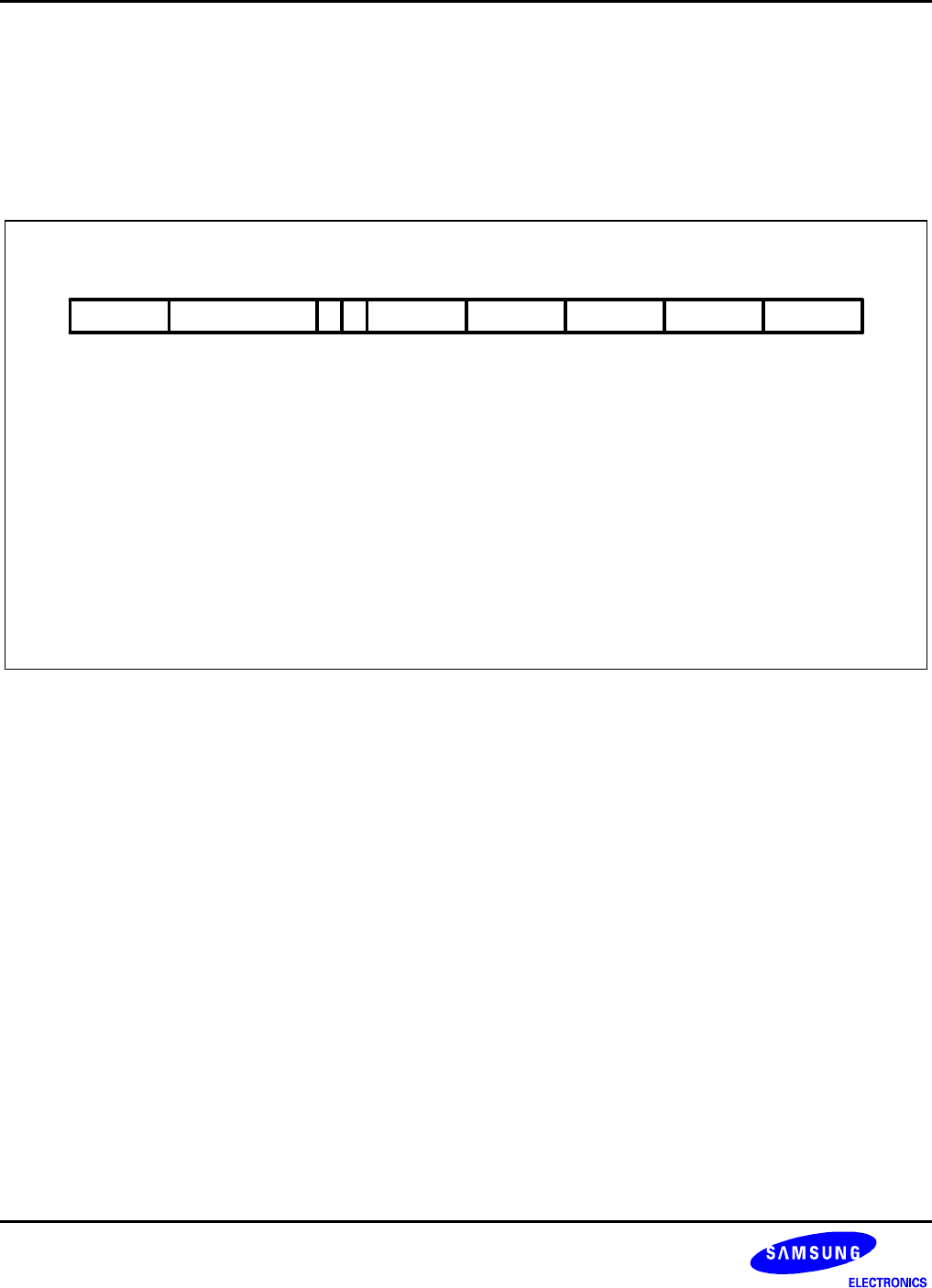

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

instruction encoding is shown in Figure 3-12.

The multiply and multiply-accumulate instructions use an 8 bit Booth's algorithm to perform integer multiplication.

31 27 19 15

Cond

28 16 111221 20

SRd Rn

[15:12][11:8][3:0] Operand Registers

[19:16] Destination Register

[20] Set Condition Code

0 = Do not after condition codes

1 = Set condition codes

[21] Accumulate

0 = Multiply only

1 = Multiply and accumulate

[31:28] Condition Field

22

1001

Rs RmA000000

87 43 0

Figure 3-12. Multiply Instructions

The multiply form of the instruction gives Rd:=Rm*Rs. Rn is ignored, and should be set to zero for compatibility

with possible future upgrades to the instruction set. The multiply-accumulate form gives Rd:=Rm*Rs+Rn, which

can save an explicit ADD instruction in some circumstances. Both forms of the instruction work on operands which

may be considered as signed (2's complement) or unsigned integers.

The results of a signed multiply and of an unsigned multiply of 32 bit operands differ only in the upper 32 bits - the

low 32 bits of the signed and unsigned results are identical. As these instructions only produce the low 32 bits of a

multiply, they can be used for both signed and unsigned multiplies.

For example consider the multiplication of the operands:

Operand A Operand B Result

0xFFFFFFF6 0x0000001 0xFFFFFF38