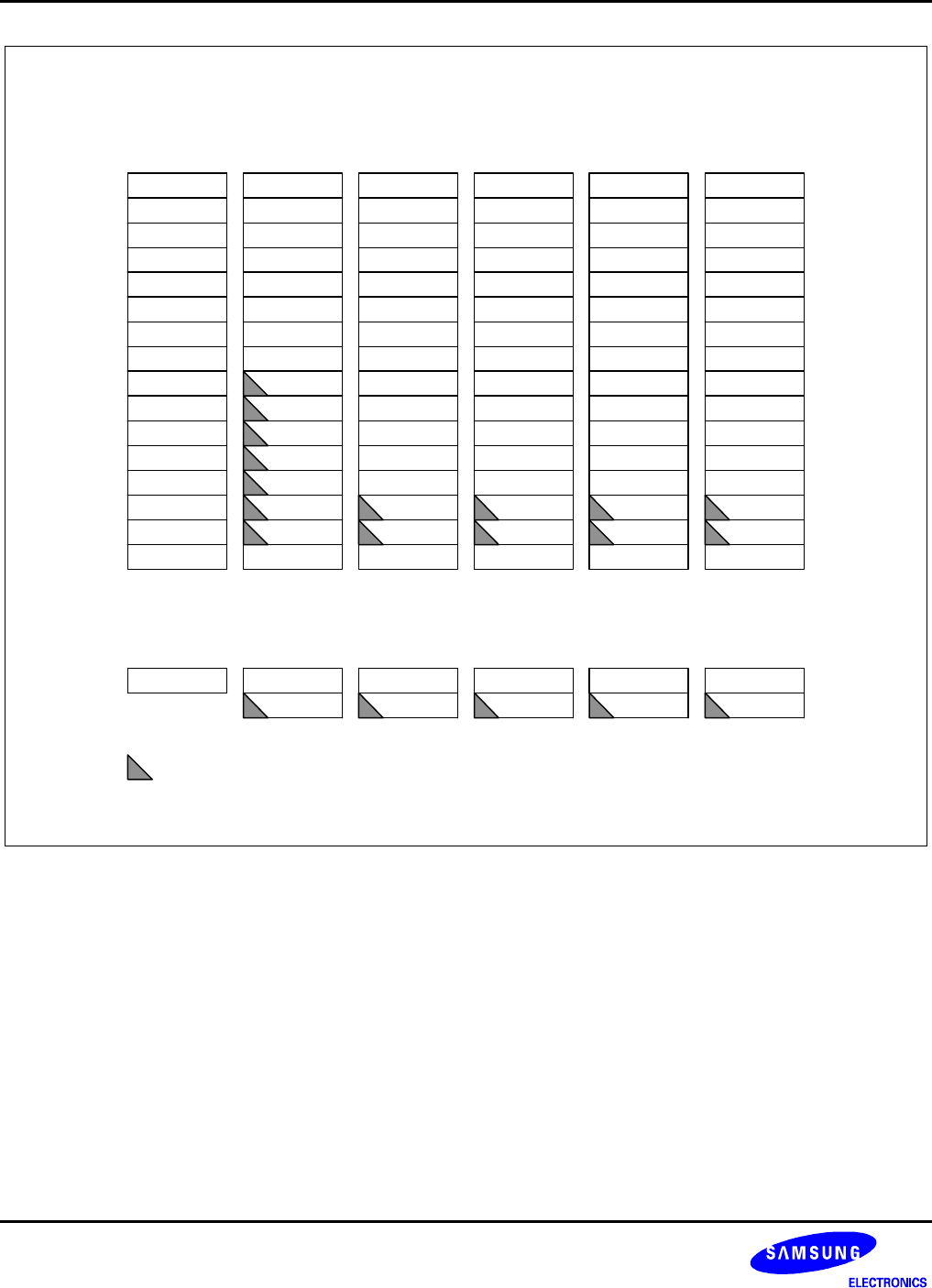

PROGRAMMER'S MODEL S3C2440A RISC MICROPROCESSOR

2-4

R0

R1

R2

R3

R4

R5

R6

R7

R9

R8

R10

R11

R12

R13

R14

R15 (PC)

R0

R1

R2

R3

R4

R5

R6

R7

R9

R8

R10

R11

R12

R13_

svc

R14_

svc

R15 (PC)

R0

R1

R2

R3

R4

R5

R6

R7

R9_

fiq

R10_

fiq

R11_

fiq

R12_

fiq

R13_

fiq

R14_

fiq

R15 (PC)

R8_

fiq

R0

R1

R2

R3

R4

R5

R6

R7

R9

R8

R10

R11

R12

R13_

abt

R14_

abt

R15 (PC)

R0

R1

R2

R3

R4

R5

R6

R7

R9

R8

R10

R11

R12

R13_

irq

R14_

irq

R15 (PC)

R0

R1

R2

R3

R4

R5

R6

R7

R9

R8

R10

R11

R12

R13_

und

R14_

und

R15 (PC)

System & User

FIQ

Supervisor IRQAbort Undefined

ARM State General Registers and Program Counter

ARM State Program Status Registers

CPSR CPSR

SPSR_

fiq

CPSR

SPSR_irq

= banked register

CPSR

SPSR_

und

CPSR

SPSR_

abt

CPSR

SPSR_

svc

Figure 2-3. Register Organization in ARM State